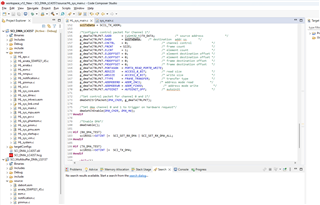

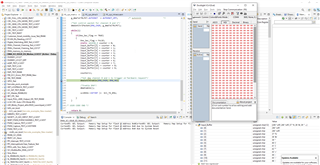

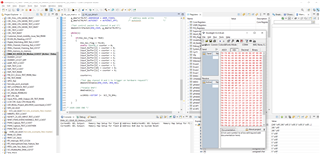

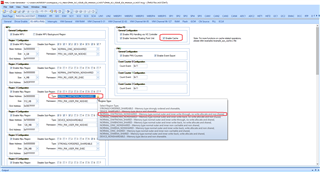

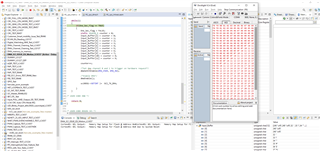

我正在使用 DMA 实现 SCI 传输、这基于 example_sci_dma.c 示例文件。 I CAN (硬件)触发要定期传输的正确字节数、但发送数据包的内容保持不变。 我已经在调试器中验证 DMA 目标地址是 SCI 发送缓冲器的正确地址、但 DMA 在 DMA 初始化时重复传输发送缓冲器的值。 换句话说、当我初始化 DMA 寄存器时、SCI-TX 缓冲区是{1,2,3,4,5,6,7,8,9}、只有这些数据通过 SCI 传输、即使 SCI-TX 存储器发生了变化。

我通过以下方式触发 DMA 传输: dmaREG->HWCHENAS = 1 (对于 DMA_CH0)。 我是否还需要执行其他操作来更新内部 DMA 存储器/FIFO?

谢谢!

吉姆