主题中讨论的其他器件:HALCOGEN

工具与软件:

从开始执行以下操作:

上述两个函数( coreInvalidateDCByAddress()和 coreCleanDCByAddress() )似乎在 Halcogen 中不可用。

从哪里可以找到这些资源?

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

从开始执行以下操作:

上述两个函数( coreInvalidateDCByAddress()和 coreCleanDCByAddress() )似乎在 Halcogen 中不可用。

从哪里可以找到这些资源?

谢谢

Paul、你好!

我与这个常见问题解答的创建者讨论了这个问题。 他提到这些函数不是由 ( coreInvalidateDCByAddress()& coreCleanDCByAddress() )由 HALCoGen 生成的。

他告诉我、这些操作可以在 cortex-R5 TRM 中找到。

e2e.ti.com/.../1067.DDI0460C_5F00_cortexr5_5F00_trm.pdf

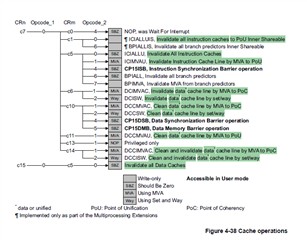

在上面的 TRM 中、请参阅第4.3.22节(缓存操作)。

这里介绍了如何执行不同的高速缓存操作:

由于这些整个操作不是由 HALCoGen 生成的、因此我们需要根据要求创建 API。

——

谢谢、此致、

Jagadish。