你好。

我尝试从 SCI 器件接收数据、并使用 DMA 将数据复制到 RAM。 我从其他设备接收到突发数据(长度未知)、并 使用周期性线程轮询复制的数据。

我建立一个 DMA 传输、将1字节作为元素大小、每帧1个元素、将帧数量作为接收缓冲区的大小(以字节为单位)、并激活 自动启动。

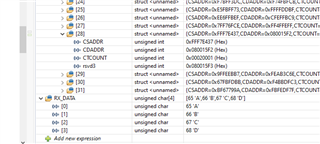

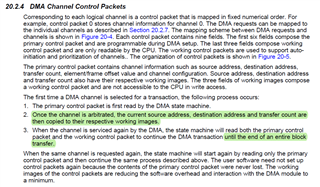

我从"20.2.4 DMA 通道控制数据包"的文档中了解到、 除非发生仲裁、否则工作控制数据包不会是最新的。 为此、我并行运行2个从 RAM 到 RAM 的8字节"虚拟"DMA 传输、 以强制对两个 FIFO 进行仲裁。 我不使用 FIFO A 或 B 中的信息、因为无法对所有 FIFO 的寄存器进行原子读取。

我观察到强制仲裁 一直有效, 但在一个特定的情况下:当传输完全填满接收缓冲,没有更多的传输发生。

我们举一个例子、我使用32字节的 接收缓冲区( 从0x80700100开始 、到 0x8070011f 结束)、启动时用0xFF 填充缓冲区。

- 接收缓冲区为: >ff ff ff ff ff ff ff ff ff FF ff ff ff ff ff ff ff ff ff ff ff FF ff ff ff ff ff ff ff ff ff ff ff FF ff ff ff ff ff ff ff ff ff ff ff FF ff ff ff ff ff ff ff ff ff ff ff FF ff ff ff ff ff ff ff ff ff ff ff FF <

- 18字节开始传输 (值从0x00到0x11)

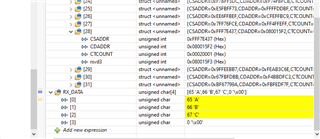

- 在传输期间、发生了一个读取操作:

接收 缓冲区 大于00 01 02 03 04 05 06 07 ff ff ff ff ff ff ff FF ff ff ff ff ff ff ff ff ff ff ff FF ff ff ff ff ff ff ff ff ff ff ff FF ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff <

工作控制数据包的 CDADDR 为0x80700108、正常。 - 传输结束后发生另一个读取操作:

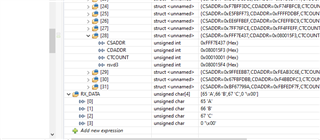

接收 缓冲区 大于00 01 02 03 04 05 06 07 08 09 0A 0b 0c 0d 0e 0f 10 11 off ff ff ff ff ff ff ff FF ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff <

工作控制数据包的 CDADDR 为0x80700112、 正常且最新。 - 另一个14字节传输开始(值从0x11到0x1E)

- 在第2个传输期间、发生了一个读取操作:

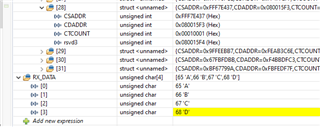

接收 缓冲器大于00 01 02 03 04 05 06 07 08 09 0A 0b 0c 0d 0e 0f 10 11 12 13 14 15 16 17 18 19 1A 1b ff <

工作控制数据包的 CDADDR 为0x8070011d、 正常。 - 传输结束后发生另一个读取操作:

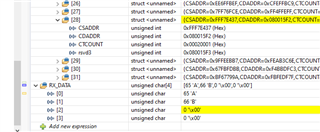

接收 缓冲器为>00 01 02 03 04 05 06 07 08 09 0A 0b 0c 0d 0e 0f 10 11 12 13 14 15 16 17 18 19 1A 1b c 1d <. 完全充满电。

工作控制数据包的 CDADDR 为0x8070011e、即 不是最新的。 (即使两个 FIFO 进行了多次仲裁)

已收到块转移完成中断。

工作控制数据包中的寄存器不会更改、直到发生另一个传输。

这种行为是否正常且预期会从 DMA 中发生、因为我在文档中没有看到有关此特定案例的任何信息?

这意味着、在任何情况下、块传输完成后工作控制数据包都不会更新。

此致