工具与软件:

您好!

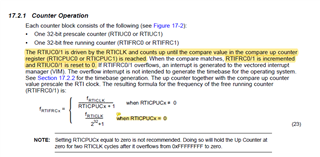

对于 RTI、我们有以下实现来 读取计时器0:

但是、对于下面提到的情况、我们认为计时器读取的值可能不正确:

当 FRC0 = 0时、URC 0 = 0xFFFFFFFF

Timer_h = STATIC_SN74(RTI_BASE[FRC0]<Uint32> );

//timer_h 为0

TIMER_l = STATIC_CAST (RTI_BASE[UC0]);

//timer_l 将为0、因为 UC0将在前一个指令(回滚)之后增加其定时器计数、即0xFFFFFFFF +1 => 0。

而且 timer_h 将为0、但期望 timer_h 应为1。

是否有 解决方案来处理这种情况 ?