主题中讨论的其他器件: HALCOGEN

工具与软件:

尊敬的所有人:

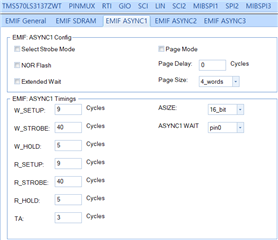

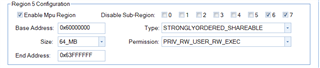

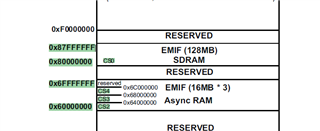

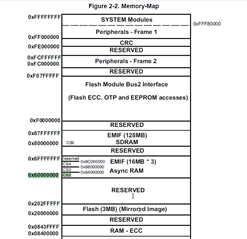

我们通过连接 TMS570LS3137和 FPGA 来进行 EMIF 通信测试。

这是一个在尝试读取 TMS570中 EMIF 区域的地址时从 FPGA 写入数据的测试。

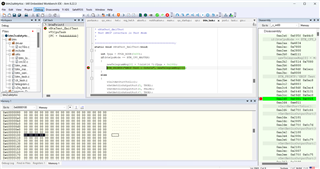

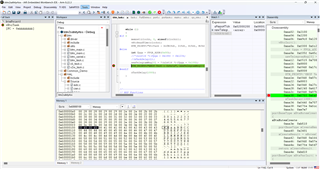

首先、我在 TMS570上简要执行了 EMIF 读取/写入测试、如下所示。

INT FPGA = FPGA_ADDR (0x00);

*(uint16 *)(FPGA + 0x100)= 0x1234;

newTelegramMsg[0]=*(uint16 *)(FPGA + 0x100);

newTelegramMsg[0]值在0x1234处正常读取。

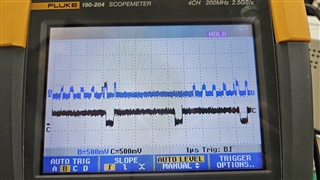

但是、TMS570和 FPGA 之间的 EMIF 测试效果不好。

原理图

newTelegramMsg[0]=*(uint16 *)(FPGA + 0x100);

该代码将为您生成一个代码

FPGA 识别 CS 和 OE 引脚、并在数据线上加载数据。 当您读取从 FPGA 发送的数据时、诸如0x40、0x41...之类的值 被读取。

这是计时问题吗?

那么我们应该怎么做呢?

此致、

IBLEE