工具与软件:

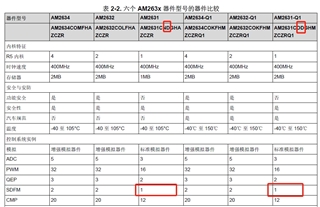

环境:CCS12.7 sdk9.0.02 我使用我自己的 PCB 与263x

在 syscfg 中配置的 SDFM0: 使用滤波器通道4、IO 设置 SDFM CLK 引脚 A15数据引脚 C14

在 syscfg 中配置的 SDFM1: 使用滤波器通道3/4、IO 设置 SDFM CLK 引脚 B13和 A13数据引脚 B12&A12

编译器和运行, 代码到波纹管,我甚至没有配置关于中断

void __attribute__((interrupt("ABORT"), section(".text.hwi"),weak)) HwiP_data_abort_handler_c(void)

{

volatile uint32_t loop = 1;

while(loop!=0U)

{

;

}

}

我的代码如下:

void init_sigmaDelta(void)

{

/* Over value threshold settings */

uint16_t hlt = 0x7FFF;

/* Under value threshold settings */

uint16_t llt = 0x0000;

/* Configure Modulator Clock rate = Modulator data rate */

SDFM_setupModulatorClock(SDFM_VBUS_BASE_ADDR, SDFM_FILTER_4, SDFM_MODULATOR_CLK_EQUAL_DATA_RATE); //VBUS

SDFM_setupModulatorClock(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_3, SDFM_MODULATOR_CLK_EQUAL_DATA_RATE);

SDFM_setupModulatorClock(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_4, SDFM_MODULATOR_CLK_EQUAL_DATA_RATE);

SDFM_enableSynchronizer(SDFM_VBUS_BASE_ADDR, SDFM_FILTER_4, SDFM_CLOCK_SYNCHRONIZER | SDFM_DATA_SYNCHRONIZER);

SDFM_selectClockSource(SDFM_VBUS_BASE_ADDR, SDFM_FILTER_4, SDFM_CLK_SOURCE_CHANNEL_CLK);

SDFM_configEnhancedComparator(SDFM_VBUS_BASE_ADDR, (SDFM_FILTER_4 | SDFM_FILTER_SINC_3 | SDFM_SET_OSR(32)), SDFM_THRESHOLD(32767,0), \

SDFM_THRESHOLD(32767,0), (SDFM_HTLZ_DISABLE | 32767));

SDFM_selectCompEventSource(SDFM_VBUS_BASE_ADDR, SDFM_FILTER_4 , SDFM_COMP_EVENT_1 , SDFM_COMP_EVENT_SRC_COMPH1);

SDFM_selectCompEventSource(SDFM_VBUS_BASE_ADDR, SDFM_FILTER_4 , SDFM_COMP_EVENT_2 , SDFM_COMP_EVENT_SRC_COMPL1);

SDFM_configDataFilter(SDFM_VBUS_BASE_ADDR, (SDFM_FILTER_4 | SDFM_FILTER_SINC_3 | SDFM_SET_OSR(128)), \

(SDFM_FILTER_ENABLE | SDFM_DATA_FORMAT_16_BIT | SDFM_SHIFT_VALUE(7)));

SDFM_enableMainFilter(SDFM_VBUS_BASE_ADDR);

SDFM_enableSynchronizer(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_3, SDFM_CLOCK_SYNCHRONIZER | SDFM_DATA_SYNCHRONIZER);

SDFM_enableSynchronizer(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_4, SDFM_CLOCK_SYNCHRONIZER | SDFM_DATA_SYNCHRONIZER);

SDFM_selectClockSource(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_3, SDFM_CLK_SOURCE_CHANNEL_CLK);

SDFM_selectClockSource(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_4, SDFM_CLK_SOURCE_CHANNEL_CLK);

SDFM_configEnhancedComparator(SDFM_UW_PHASE_BASE_ADDR, (SDFM_FILTER_3 | SDFM_FILTER_SINC_3 | SDFM_SET_OSR(32)), SDFM_THRESHOLD(32767,0), \

SDFM_THRESHOLD(32767,0), (SDFM_HTLZ_DISABLE | 32767));

SDFM_selectCompEventSource(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_3 , SDFM_COMP_EVENT_1 , SDFM_COMP_EVENT_SRC_COMPH1);

SDFM_selectCompEventSource(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_3 , SDFM_COMP_EVENT_2 , SDFM_COMP_EVENT_SRC_COMPL1);

SDFM_configEnhancedComparator(SDFM_UW_PHASE_BASE_ADDR, (SDFM_FILTER_4 | SDFM_FILTER_SINC_3 | SDFM_SET_OSR(32)), SDFM_THRESHOLD(32767,0), \

SDFM_THRESHOLD(32767,0), (SDFM_HTLZ_DISABLE | 32767));

SDFM_selectCompEventSource(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_4 , SDFM_COMP_EVENT_1 , SDFM_COMP_EVENT_SRC_COMPH1);

SDFM_selectCompEventSource(SDFM_UW_PHASE_BASE_ADDR, SDFM_FILTER_4 , SDFM_COMP_EVENT_2 , SDFM_COMP_EVENT_SRC_COMPL1);

SDFM_configDataFilter(SDFM_UW_PHASE_BASE_ADDR, (SDFM_FILTER_3 | SDFM_FILTER_SINC_3 | SDFM_SET_OSR(128)), \

(SDFM_FILTER_ENABLE | SDFM_DATA_FORMAT_16_BIT | SDFM_SHIFT_VALUE(7)));

SDFM_configDataFilter(SDFM_UW_PHASE_BASE_ADDR, (SDFM_FILTER_4 | SDFM_FILTER_SINC_3 | SDFM_SET_OSR(128)), \

(SDFM_FILTER_ENABLE | SDFM_DATA_FORMAT_16_BIT | SDFM_SHIFT_VALUE(7)));

SDFM_enableMainFilter(SDFM_UW_PHASE_BASE_ADDR);

}

和主循环:

int main(void)

{

System_init();

Board_init();

init_sigmaDelta();

while(1);

Board_deinit();

System_deinit();

return 0;

}

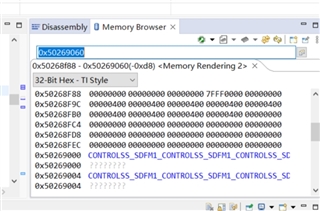

当我删除 sdfm0或 sdfm1时、 代码运行正常、 无论通道如何匹配、我都尝试了多次、只要 同时配置2个 SDFM、就会发生错误。

当我在 评估板上运行代码时、一切都正常、包括2个 SDFM 一起工作、但在我自己的板上、2个 SDFM 无法一起配置、 这是为什么? 我运行了 SPI/PWM/UART/ADC/DAC 等其他外设、……除了2个 SDFM 一起配置外、其他一切都正常