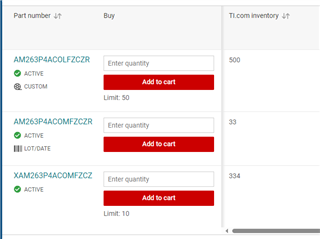

主题中讨论的其他器件:UNIFLASH、 AM263P4、AM2634

工具与软件:

你(们)好

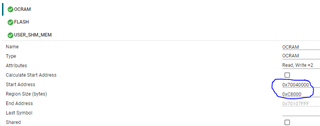

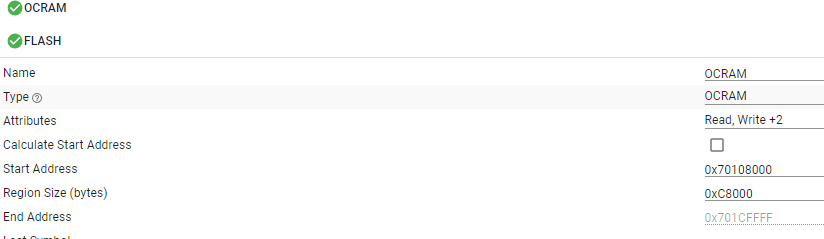

应该如何为锁步情况定义 OCRAM 存储器区域?

从文档中我了解到 TCM 翻倍、如果第二个 CPU 没有映像、QSPI SBL 将自动切换到锁步模式。

在这种情况下、两个处于锁步模式的 CPU 是否具有相同的 OCRAM 区域?

检查了显示锁步错误机制的示例: CCM 、但 OCRAM 不共享、并且 targetconfigs 似乎不完整(在任何位置至少没有设置辅助标志或其他标志、所有四个内核都处于活动状态)。

是否有更好的示例或应用手册显示 CPU 以锁步模式运行时的 RAM 区域?

外部存储器也是一个主题、因为我们可能被迫使用 GPMC。

此致、

Barna cs.