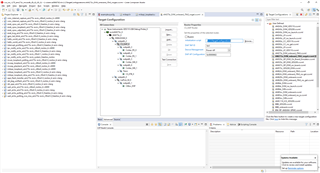

工具与软件:

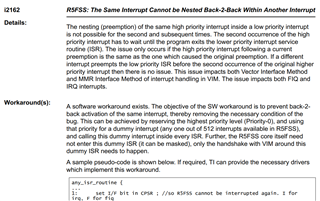

当一个低优先级 IRQ 中断继续执行时、一个高优先级中断只能被中断一次

Premise:系统中只有两个不同的优先级周期定时器可以中断 IRQ1和 IRQ2、而 IRQ1的优先级高于 IRQ2;

Operation:在 IRQ1中执行相对较长的延迟、以确保 IRQ2在延迟周期;内可被多次触发

现象:无论 IRQ2延迟事件持续多长时间、IRQ1在 IRQ2延迟期间只能触发一次中断;

这种现象不符合对中断嵌套的传统理解。 如果 AM2732对该器件有特殊要求、请进行说明。 否则、请协助解释这种现象的原因和解决方法。 谢谢。