工具与软件:

您好 Jagasish、

我需要回到这个主题。 我使用 TMS570LS1224的 EEPROM 扇区作为 EEPROM 仿真、现在使用我自己的 Wear leveinig 算法已经有很多年了、到目前为止它都能正常工作。 现在、我要 EEC 功能、以在 FEE 损坏时获得 ESM 异常。

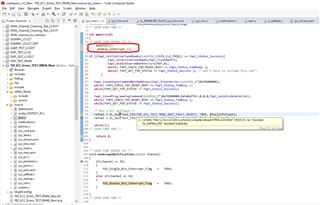

因此、我使用 Fapi_Auto EccGeneration 模式和8字节的多字节来向费编写 wehn。

Fapi_issueProgrammingCommand ((uint32_t*) u32_Addr、&(u8_Buffer[0])、u8_idx、NULL、0、 Fapi_Auto E.ccGeneration)

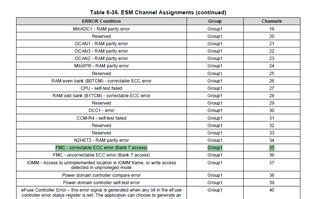

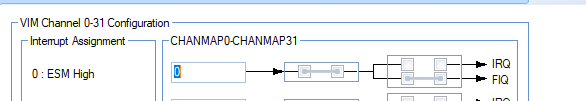

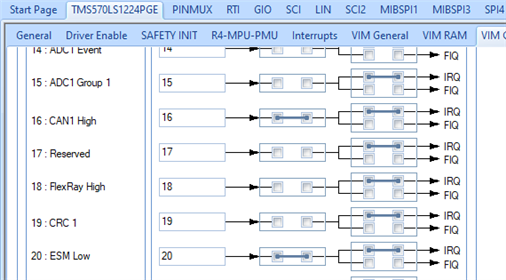

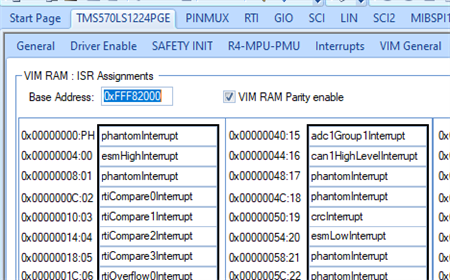

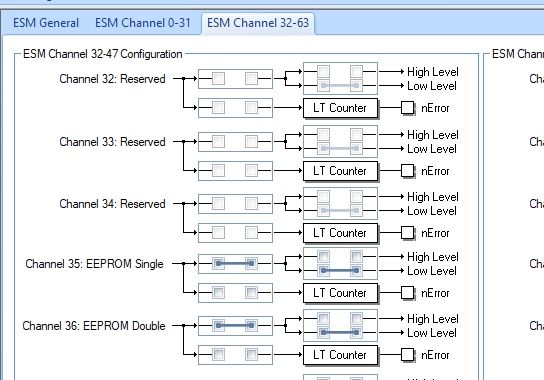

我按如下方式配置了 ESM:

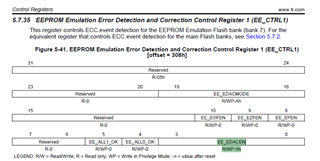

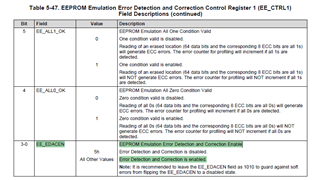

我已尝试启用 ECC 错误检测功能

Fapi_Fmc 4.0类型* p_FmcRegisters = F021_CPU0_BASE_ADDRESS;

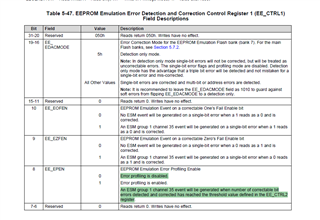

P_FmcRegisters->EeCtrl2.EE_CTRL2_BITS.EE_SEC_THRESHOLD = 1;

P_FmcRegisters->EeCtrl1.EE_CTRL1_BITS.EE_EDACMODE = 0x05; //仅检测模式

P_FmcRegisters->EeCtrl1.EE_CTRL1_BITS.EE_EOFEN = 1; //将在其上生成 ESM 组1通道35事件

//当一读取为0并被校正时出现一位错误

P_FmcRegisters->EeCtrl1.EE_CTRL1_BITS.EE_EZFEN = 1; //将在其上生成 ESM 组1通道35事件

//当零读取为1时出现一位错误并被纠正

P_FmcRegisters->EeCtrl1.EE_CTRL1_BITS.EE_PEN = 1; //已启用错误分析。

//在编号时将生成 ESM 组1通道35事件

//已检测到和已校正的可纠正位错误

// EE_CTRL2寄存器中定义的阈值。

P_FmcRegisters->EeCtrl1.EE_CTRL1_BITS.EE_All1_OK = 1; //读取已擦除位置(64个数据位及其相应的值)

// 8个 ECC 位都为1)将不会生成 ECC 错误。

//分析的错误计数器不会递增 if

//检测到所有数字。

P_FmcRegisters->EeCtrl1.EE_CTRL1_BITS.EE_EDACEN = 0x0a; //已启用错误检测和校正

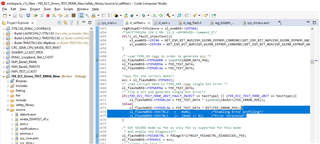

并尝试在 Hercules Safety_Lib 的帮助下触发 ESM 异常:

sl_Sel4.12.7Fe_stResult Test_Result;

bool b_result = false;

B_Result = SL_SelfTest_FEE (FEE_ECC_TEST_MODE_1bit_FAULT_INJECT、FALSE、&FEE_stResult);

B_Result = SL_SelfTest_FEE (FEE_ECC_TEST_MODE_2BIT_FAULT_INJECT、FALSE、&FEE_stResult);

sl_SelfTest_FEE()的调用返回 true、但是 FEE_stResult 为 ST_FAIL、并且我没有得到 ESM 异常。

我该怎么做?

此致

Jens