主题中讨论的其他器件:HALCOGEN

工具与软件:

您好!

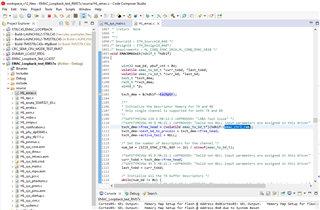

我使用 HalCoGen 提供的 EMACHWInit API 初始化了 EMAC 但是、在我写入 调用 EMACTransmit 函数后、我没有看到传输被触发。 我在写入 DMA 描述符的基址后检查了 Tx0HDR、它会保持不变、在写入后从未返回零以指示初始化可能存在一些问题? 我们将感谢您提供任何有用的指示。

Thansk,

Ravi

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

我使用 HalCoGen 提供的 EMACHWInit API 初始化了 EMAC 但是、在我写入 调用 EMACTransmit 函数后、我没有看到传输被触发。 我在写入 DMA 描述符的基址后检查了 Tx0HDR、它会保持不变、在写入后从未返回零以指示初始化可能存在一些问题? 我们将感谢您提供任何有用的指示。

Thansk,

Ravi

尊敬的 Ravi:

首先、我想建议您参考 Loopback_Tx HALCoGen 中提供的"EMAC_3612"示例。 请按照以下主题了解如何访问此示例:

(4) TMS570LC4357:TMS570LC4357微控制器 HARCULIS 开发套件-基于 Arm 的微控制器论坛-基于 Arm 的微控制器- TI E2E 支持论坛

——

谢谢、此致、

Jagadish。

尊敬的 Jagadish:

感谢您的响应。

我终于找到了这个问题。 事实上、我错过了一些 pinmux 寄存器配置。 现在、当我写入 Tx0HDR 寄存器时、EMAC 似乎会启动传输并生成 Tx 中断。 但是、我没有看到数据包显示在 Wireshark 上。 我正在发送由 FreeRTOS TCP/IP 堆栈生成的 DHCP 请求数据包。 有什么想法、问题可能出在哪里?

Ravi

尊敬的 Ravi:

您能否确保您按照下面的主题中提到的步骤操作:

如果您使用的是 HDK 电路板、请参考我在上方主题中的第一条评论、否则、如果您使用的是 launchpad、请参考第二条评论。

——

谢谢、此致、

Jagadish。

e2e.ti.com/.../rm57_5F00_bare.rar

尊敬的 Jagadish:

我已附加该项目。

Ravi

尊敬的 Jagadish:

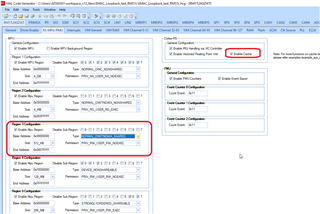

我想我已经弄清楚了问题所在。 它与缓存有关。 当我恰好在通过写入 Tx0HDR 寄存器进行传输之前刷新缓存中的 Tx 缓冲区地址时、该方法似乎有效。 不过这很奇怪、因为我将 TX 缓冲区区域标记为 NORMAL_OINC_SHARED、这意味着在 MPU 设置下的区域15 (这是用户可在 HalCoGen 中配置的最高优先级区域)中不可缓存和可共享、但似乎没有什么帮助。 我也尝试过 device_sharable、但即使这似乎没有帮助。 有什么指针吗?

Ravi

尊敬的 Ravi:

我认为 NORMAL_OINC_SHARED 不会阻止缓存。 我们应该需要将相应的存储器配置为 WRITE Through (WT)。

请参阅我的以下主题:

我在这里以一个示例进行了说明。

——

谢谢、此致、

Jagadish。

尊敬的 Jagadish:

您能否详细说明 NORMAL_OINC_SHARED 不会阻止缓存的含义? 在 HalCoGen 中、当我将光标悬停在 NORMAL_OINC_SHARED 上时 、它会将存储器区域标记为不可缓存、并在总线主器件(在本例中为 CPU 和 EMAC DMA)之间共享。 我附上了这张截图。

我曾尝试过您的建议、将内存区域标记为 NORMAL_OIWNOW_SHARED、但这似乎没有帮助。 它的唯一工作方式是完全禁用高速缓存。

Ravi

尊敬的 Ravi Teja:

您能提供您的测试代码吗

配置直写应防止缓存一致性问题。 请参阅以下常见问题解答、详细了解缓存一致性问题。

——

谢谢、此致、

Jagadish。

给你。

e2e.ti.com/.../5282.rm57_5F00_bare.rar

Ravi

尊敬的 Ravi:

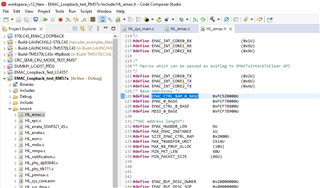

我现在讨论的是下面的 EMAC RAM 区域

这是发送和接收缓冲描述符将被正确存储的区域。我的意思是 DMA 将会读取这个描述符并且会在调用 EMACTransmit 函数后对数据进行必要的传输。

因此、我认为您没有将此区域配置到 WT 中(直写)、而是将 WT 配置到将存储数据的 RAM 区域。

今天、我再次使用以下配置进行了测试

我在这里将 WT 配置为将数据被存储的唯一 RAM 区域、并且仍然获得接收中断。

我曾尝试将内存区域标记为 NORMAL_OIWNOW_SHARED 的建议、但这似乎没有什么帮助。 它的唯一工作方式是完全禁用高速缓存。

刚才、我还尝试了启用缓存的配置、并且运行正常(我获得了接收中断)

现在,我不明白为什么这在你的终端失败了? 您的配置是否与我所做的一样?

——

谢谢、此致、

Jagadish。

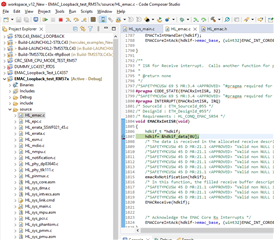

尊敬的 Ravi:

可能会发生这种情况! 由于如果您验证了 EMACTransmit 函数的定义、我们就不会对数据传输进行任何轮询、而是只为 EMAC 缓冲区描述符分配需要发送的输入数据、我们将使用此函数。

因此、这意味着完整的数据传输不会在该函数中或在此函数之后发生。 传输将在后台进行。 您甚至可以 在之前的传输完成前调用另外一个 EMACTransmit 函数、如果我们这样做的话、数据就不会丢失、而是在上一个缓冲区描述符后立即将输入数据分配给某些其他缓冲区描述符、在后台进行数据传输。

这就是 在设置 EMACTransmit 函数之后未命中 Rx 处理程序中断点的原因。

——

谢谢、此致、

Jagadish。

尊敬的 Ravi:

我在第一个传输调用之后放置了无限 while 循环、我仍然看到这个问题。

我没有看到任何这样的问题在我的最后

正如您在下图中看到的、我在第一次传输后一直保持无限循环、

您可以看到仍收到 EMAC Rx 中断。

这里是我的代码供您参考:

e2e.ti.com/.../EMAC_5F00_Loopback_5F00_test_5F00_RM57x.zip

——

谢谢、此致、

Jagadish。