工具与软件:

您好:

我们使用 mibspi_loopback_dma_am273x-evm_r5fss0-0_freertos_ti-arm-clang 的演示工程配置 TJA1145 cantrancv。

注释代码 状态= MIBSPI_enableLoopback (gMibspiHandle[CONFIG_MIBSPI0]、LOOPBACK);禁用环回功能

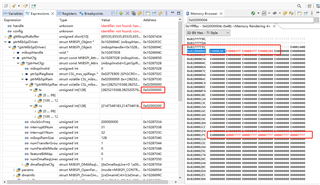

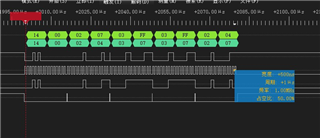

我们可以在 SPI MISO 和 MOSI 总线上找到 TX 和 RX 数据、但 RXSRAM 中为 err。

另一个实验不 注释代码 状态= MIBSPI_enableLoopback (gMibspiHandle[CONFIG_MIBSPI0]、loopback);启用环回功能、 RXSRAM 数据是正确的。

此外,之前关于 PMIC I 请求的 e2e 案例。 使用相同的演示工程和用作 mibspib 的 SPI 会很有用。

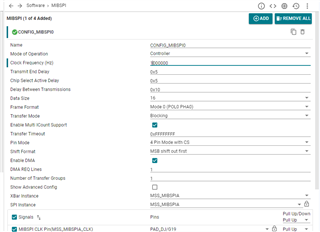

将 宏定义和变量更改如下:

#define APP_MIBSPI_MSGSIZE 10.

uint16_t gMibspiTxBuffer1[APP_MIBSPI_MSGSIZE];

uint16_t gMibspiRxBuffer[APP_MIBSPI_MSGSIZE];

uint16_t gMibspiTxBuffer[]=

{

// 0x03ff、// Reg 1 Mode control (寄存器1模式控制)

0x1400、// Reg:0x0A 锁定控制。 SPI 写访问使能

0x0207、//寄存器1模式控制

0x03ff、// Reg 1 Mode control (寄存器1模式控制)

0x03ff、// Reg 1 Mode control (寄存器1模式控制)

0x0204、//寄存器1模式控制

0x03ff、// Reg 1 Mode control (寄存器1模式控制)

0x03ff、// Reg 1 Mode control (寄存器1模式控制)

0x0207、//寄存器1模式控制

0x03ff、// Reg 1 Mode control (寄存器1模式控制)

0x03ff、// Reg 1 Mode control (寄存器1模式控制)

};

内存:

SYSCFG:

SPI 总线:

3Q。