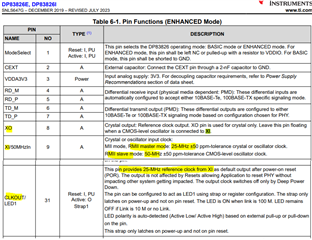

主题中讨论的其他器件:DP83826E、 SysConfig

工具与软件:

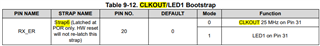

我正在尝试在定制 PCB 上使用 DP83826E 启动 CPSW。

到目前为止、我已经能够绑定驱动程序、但无法成功建立链路状态。

CPSW 驱动程序正在配置 PHY、然后进入 FSM 状态 ENETPHY_FSM_STATE_NWAIT_WAIT。

这最终会导致 EnetPhy_phyTimeout() 和 FSM 状态 ENETPHY_FSM_STATE_FOUND。 然后重复过程配置、并重新开始自动协商等待。

我添加了一些内容 debugP_log() 有助于进行故障排除的 printfs。 这些打印 BMCR、BMSR:enetphy.c 中的寄存器 这些 printfs 采用十六进制格式、具体请参阅此处:

[Cortex_R5_1]===============

CPSW LWIP TCP 客户端

================

u32IdRead:10、10、0

启动 lwIP。 Enet if Up 事件。 本地接口 IP:192.168.1.253

正在等待网络启动...

BMCR,BMRS:3,100,7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

正在等待网络启动...

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

BMRS:7849.

注意:打印:

u32IdRead:10、10、0

表示 PHYIDR1、PHYIDR2寄存器已成功读取10次、每次读取的值与 DP83826数据表中指定的值匹配时。

我已经尝试与链接伙伴链接:

TL-SG105–简单开关

Windows PC -计算机

两个链路伙伴已成功用于许多其他以太网测试。 我还尝试交换了 Cat6以太网电缆。 ‘电缆也是"已知良好"电缆。

为了便于参考、我解码了 BMCR 和 BMSR 寄存器。

这是停止时的调试视图 EnetPhy_nwayStartState ():

问题1:

我在 PHY 配置中缺少什么吗?

Q1b:

是否有任何其他有用的寄存器可以进行分析?

问题2:

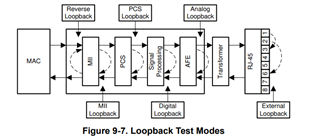

我正在考虑将环回测试功能添加到我的项目中。 您是否认为模拟环回是进行故障排除的有效方法?

问题3:

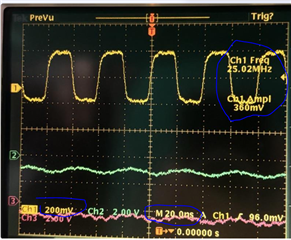

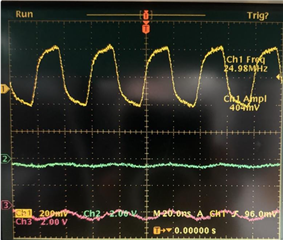

我正在考虑探测 MDI、以查看是否存在自动协商。 示波器可能无法解码信号 TD+ TD- RD+ RD-信号、但我认为应该能够检测是否发生传输。

探测 MDI 对于故障排除是否有用?

问题4:

您是否可以推荐此处未提及的任何其他故障排除措施?