主题中讨论的其他器件: SysConfig

工具与软件:

您好、TI

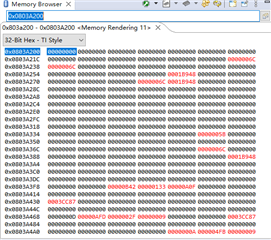

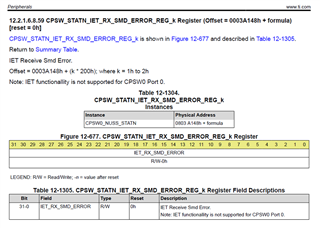

我们将使用 LP-AM243测试 CPSW 端口、我们删除了一个之前连接到 RGMII1的以太网 Phy、并将其替换为我们的 FPGA、RGMII1 TX 通道不会连接到 FPGA、因为我们不会将数据发送到 FPGA。 我们希望从 FPGA 接收广播以太网帧、但什么都没有得到。

我该如何调试这个问题、您能给我们一些建议吗、

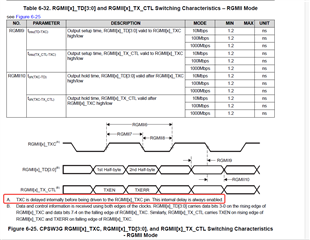

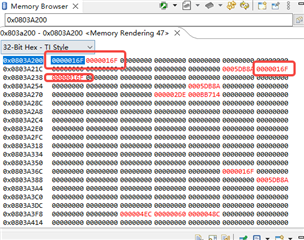

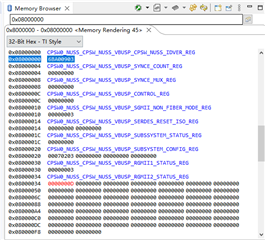

RGMII1的寄存器状态为3、这意味着100Mbps、μ s

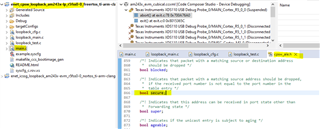

我们将在 SDK 中使用演示 enet_lwip_cpsw、并修改函数

这是我们的测试用例、请查看。

这是我们的测试用例、请查看。