主题中讨论的其他器件:SysConfig

工具与软件:

你(们)好

我可以为我的用例提供建议吗?

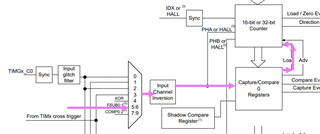

我希望在没有 CPU 中断的情况下同步每个 TIMG 计数器。

因此我想使用通用事件路由(订阅者和发布者端口)作为同步信号。

要设置是否 CC0接收订阅事件、请生成 TIMG 计数器 reset (Load)。

但它不起作用。

我可以提供建议吗?

我要做的是:

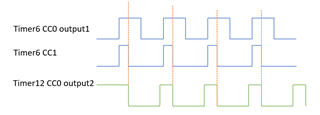

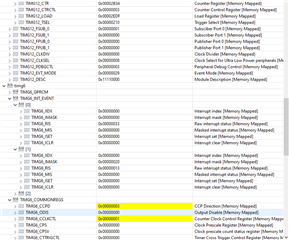

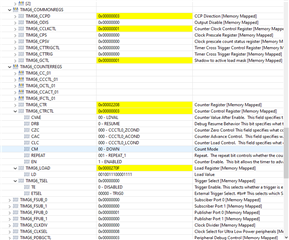

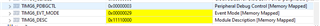

TIMG6 CC1加载事件-->事件路由 ID1 --> TIMG12 CC0输入源(IFCTL[0])--> CC0 比较事件(计数器= 1)--> CC0生成加载事件--> TIMG12计数器复位(加载)

我在 CCS 调试模式下检查了 TIMG6生成加载事件。

(如果连接通用路由、无法设置加载事件标志寄存器、可能我认为接收器清除标志会自动设置)

// clock divider

TIMG12->CLKDIV |= GPTIMER_CLKDIV_RATIO_DIV_BY_1; // div = /1, MCLK 80MHz

// clock source

TIMG12->CLKSEL |= GPTIMER_CLKSEL_BUSCLK_SEL_ENABLE; // TIMG6 bus clock is MCLK(80MHz). Please see Datasheet

//clock 2nd prescaler

TIMG12->COMMONREGS.CPS |= GPTIMER_CPS_PCNT_MASK & 0x00; // prescale /(8bit+1), dividing 1

// counter register

TIMG12->COUNTERREGS.CTRCTL = 0x00000000; // reset

TIMG12->COUNTERREGS.CTRCTL |= GPTIMER_CTRCTL_CVAE_ZEROVAL; // when module enabling, countor value set to zero

TIMG12->COUNTERREGS.CTRCTL |= GPTIMER_CTRCTL_CM_DOWN; // Count down mode

TIMG12->COUNTERREGS.CTRCTL |= GPTIMER_CTRCTL_REPEAT_REPEAT_1; // Repeat mode

TIMG12->COUNTERREGS.CTRCTL |= GPTIMER_CTRCTL_EN_DISABLED; // Timer counter disable

// load counter register, using full 16-bit

TIMG12->COUNTERREGS.LOAD |= 0x0000FFFF;

// event

// come from Channel ID1(TIMG6)

//FSUB_0 port

TIMG12->FSUB_0 |= (GPTIMER_FPUB_0_CHANID_MASK & 0x01); // connect channel ID1

// TIMG12->COUNTERREGS.IFCTL_01[0] |= GPTIMER_IFCTL_01_ISEL_FSUB0; //input source = FUSB_0

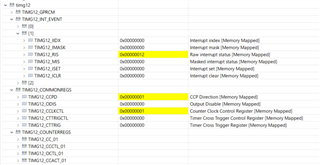

//setting of crosstriger

TIMG12->COMMONREGS.CTTRIGCTL |= GPTIMER_CTTRIGCTL_EVTCTTRIGSEL_FSUB0; //trigger from FSUB0

TIMG12->COMMONREGS.CTTRIGCTL |= GPTIMER_CTTRIGCTL_EVTCTEN_ENABLE; //input crosstrigger enable

TIMG12->COUNTERREGS.TSEL |= GPTIMER_TSEL_TE_ENABLED; // trigger enable

TIMG12->COUNTERREGS.TSEL |= GPTIMER_TSEL_ETSEL_TRIG_SUB0; // trigger from FSUB0

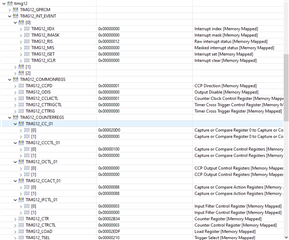

//setting CC0 imput source

TIMG12->COUNTERREGS.IFCTL_01[0] |= GPTIMER_IFCTL_01_ISEL_TRIG_INPUT; //input source = trigger

//setting CC0

TIMG12->COUNTERREGS.CC_01[0] |= (GPTIMER_CC_01_CCVAL_MASK & 0x1); // compare value

TIMG12->COUNTERREGS.CCCTL_01[0] |= GPTIMER_CCCTL_01_COC_CAPTURE; // capture mode

TIMG12->COUNTERREGS.CCCTL_01[0] |= GPTIMER_CCCTL_01_CCOND_CC_TRIG_RISE; //capture rising edge

TIMG12->COUNTERREGS.OCTL_01[0] |= GPTIMER_OCTL_01_CCPO_LOAD; // output load event

// Capture or Compare (CCP) setting

TIMG12->COMMONREGS.CCPD |= GPTIMER_CCPD_C0CCP1_OUTPUT; // TIMG12_CCP1 output

TIMG12->COMMONREGS.ODIS &= ~(GPTIMER_ODIS_C0CCP1_MASK); // CCP1 is output, not forced Low

TIMG12->COUNTERREGS.CC_01[1] |= (GPTIMER_CC_01_CCVAL_MASK & 135); // compare value

TIMG12->COUNTERREGS.CCCTL_01[1] |= GPTIMER_CCCTL_01_COC_COMPARE; // Compare mode

TIMG12->COUNTERREGS.OCTL_01[1] |= GPTIMER_OCTL_01_CCPIV_LOW; // initvalue = low output

TIMG12->COUNTERREGS.OCTL_01[1] |= GPTIMER_OCTL_01_CCPOINV_INV; // output is inversion

TIMG12->COUNTERREGS.OCTL_01[1] |= GPTIMER_OCTL_01_CCPO_FUNCVAL; // Output source = Signal generator value

TIMG12->COUNTERREGS.CCACT_01[1] |= GPTIMER_CCACT_01_LACT_CCP_LOW; // Load event = set Low

TIMG12->COUNTERREGS.CCACT_01[1] |= GPTIMER_CCACT_01_CDACT_CCP_HIGH; // Compare event = set high

// enabling clock

TIMG12->COMMONREGS.CCLKCTL |= GPTIMER_CCLKCTL_CLKEN_ENABLED; // clock enabled

//Before main roop

TIMG6->COUNTERREGS.CTRCTL |= GPTIMER_CTRCTL_EN_ENABLED; // Timer counter enable

TIMG12->COUNTERREGS.CTRCTL |= GPTIMER_CTRCTL_EN_ENABLED; // Timer counter enable

CC 比较值为0x1、因此如果有接收到一个事件将生成比较事件。

如果它按我认为的方式工作、则 TIMG12CC1输出周期必须与 TIMG6 PWM 相同。

(加载值为 TIMG12>TIMG6、因此 TIMG6在 TIMG12 PWM 优先级之前生成加载事件(=作为 TIMG12加载事件发送)。 因此每个引物将是相同的)

谢谢!

Gr