Other Parts Discussed in Thread: MSPM0G1107, MSPM0G1505, MSPM0G1506, MSPM0G3505, MSPM0L1228, MSPM0L2227, MSPM0L1105, MSPM0G1105, MSPM0G1106, MSPM0G1507, MSPM0G3105, MSPM0G3106, MSPM0G3107, MSPM0G3506, MSPM0G3507, MSPM0L1227, MSPM0L2228

主题中讨论的其他器件: MSPM0G1105、 MSPM0G1106、MSPM0G1107 、MSPM0G1505 、MSPM0G1506、 MSPM0G1507、 MSPM0G3105、 MSPM0G3106、 MSPM0G3107、MSPM0G3505 、 MSPM0G3506、 MSPM0G3507、 MSPM0L1227、MSPM0L1228 、MSPM0L2227 、 MSPM0L2228

工具与软件:

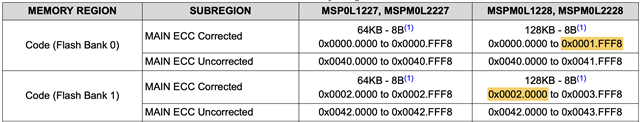

MSPM0L1105的数据表指出:

CPU 访问闪存区域最后8个字节之一将导致硬故障。 这是因为预取逻辑会尝试提前读取一个闪存字(64位)、导致对无效存储器位置的读取尝试。

这是否只涉及指令访问、或者这是否也适用于数据访问? 数据访问是否具有预取逻辑、会导致 CPU 读取的数据多于所请求的数据?