工具与软件:

您好、TI 专家:

我使用 AM243X EVM 板作为 RC 来访问 FPGA EP。

现在、我将重点介绍如何进行访问异常处理。 我进行以下测试。

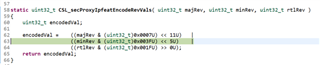

1跨境访问--我读取了一个地址,从 EP 的存储器范围之外,MCU 崩溃(程序跳转到 CSL_secProxyIpEncoderRevVals()并停留在那里,如下图所示)。

2当 EP 不存在时访问--在初始化之后、RC 可以访问 EP、然后关闭 EP。 如果 RC 访问 EP、MCU 也将崩溃、这与前一个测试的结果相同。

对于跨境访问、我可能会在访问前检查地址。 所以、这很容易避免。

我的问题是第二个问题、在进行任何访问之前、RC 如何知道 EP 是否处于运行状态?

是否检查某些寄存器(如 LtsmsgState)?

或者、根据 TRM 的"12.2.2.4.4.6.3链路 断开中断"说明、当断开连接发生时、将有一个 PCIe_LINK_STATE_PULSE 中断、我如何启用该中断?

谢谢您、BR

Chunyang