工具与软件:

嗨、团队:

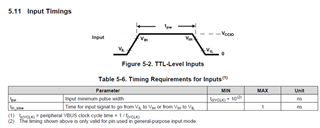

根据数据表、VIL 和 VIH 之间的上升/下降时间指定为 tin_SLEW=1nsmax。

Q1:这是否意味着 MCU 输入电压的上升/下降时间 必须小于1ns?

Q2:所有输入端子是否都必须满足这些规格?

Q3:如果上升/下降时间超过1ns、那么运行是否会出现问题?

此致

大桥

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

嗨、团队:

根据数据表、VIL 和 VIH 之间的上升/下降时间指定为 tin_SLEW=1nsmax。

Q1:这是否意味着 MCU 输入电压的上升/下降时间 必须小于1ns?

Q2:所有输入端子是否都必须满足这些规格?

Q3:如果上升/下降时间超过1ns、那么运行是否会出现问题?

此致

大桥

你好、大桥

[报价 userid="520939" url="~/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/1432689/rm46l430-input-timing-requirement ]Q1:这是否意味着 MCU 输入电压的上升/下降时间 必须小于1ns?上升/下降时间应小于1ns。

[quote userid="520939" url="~/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/1432689/rm46l430-input-timing-requirement 问:所有输入终端是否都必须符合这些规范?是的、所有 GPIO 输入端子都应满足此要求。

[quote userid="520939" url="~/support/microcontrollers/arm-based-microcontrollers-group/arm-based-microcontrollers/f/arm-based-microcontrollers-forum/1432689/rm46l430-input-timing-requirement Q3:如果上升/下降时间超过1ns、操作是否有问题?它会导致 IO 单元额外老化。 信号位于 VoH/Vol 中间范围的时间越长、在电压缓冲器上就会出现更多磨损。

——

谢谢、此致、

Jagadish。

尊敬的 Jagadish:

感谢您的支持。

这会导致 IO 单元额外老化。 信号在 VoH/Vol 中间范围内的时间越长、在电压缓冲器上就会出现更多磨损。

为什么 Voh/Vol 中频段的信号给电压缓冲器造成磨损?

此致

大桥

你好、大桥

当设备处于"未定义状态"时、*消耗的电量可能比平时多得多(可能导致设备死亡)。 这是因为在这种状态下、芯片内的某些电路元件全部"导通"、基本上在 Vcc 和 Vss 之间产生一个死短路。 因此在大多数数字 IC 上必须避免这种情况。

您可以一次性参阅以下链接以了解更多详细信息吗:

数字逻辑-当电压处于不确定的区域时会发生什么情况? -电气工程堆栈交换

为什么 TTL 和 CMOS 电路在0和1逻辑之间具有不确定区域? - Quora.

——

谢谢、此致、

Jagadish。

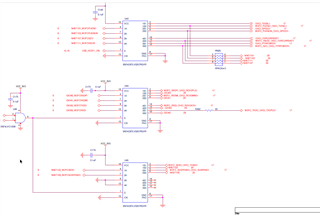

尊敬的 Ryoma:

对于响应延迟、我们深表歉意、

我们在原理图中使用了一些 SN74xx 系列多路复用器等。

我想您可以将这些器件用于您的实施。

您可以通过以下链接查看我们的原理图:

LAUNCHXL2-RM46开发套件|德州仪器 TI.com

——

谢谢、此致、

Jagadish。