主题中讨论的其他器件:AB15

工具与软件:

你好

我在 EPI 总线的初始化方面遇到问题。 该总线被配置为访问两个存储器器件。

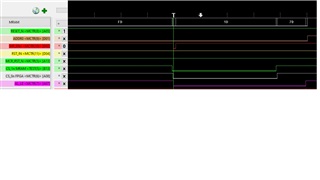

我看到的是、在 EPI 总线初始化时、我会收到写使能信号和片选有效信号、这会导致对器件执行不必要的写入操作。

不过、还没有尝试实际对器件执行写入操作。

请参阅写使能脉冲(WR_ENn、引脚 PN2)图

片选 CS_1n MRAM。

这是 EPI 初始化函数的代码、如果在启动时调用此函数、则会触发上述事件、从而导致对器件进行不必要的写入。

我在这里做错了什么。

int EPI_TCPIP_init (void)

{

INT STATUS = 1;

/*启用 EPI 所需的 GPIO 端口的时钟*/

MAP_SysCtlPeripheralEnable (SYSCTL_PERIPH_GPIOA);

MAP_SysCtlPeripheralEnable (SYSCTL_PERIPH_GPIOB);

MAP_SysCtlPeripheralEnable (SYSCTL_PERIPH_GPIOC);

MAP_SysCtlPeripheralEnable (SYSCTL_PERIPH_GPIOG);

MAP_SysCtlPeripheralEnable (SYSCTL_PERIPH_GPIOH);

MAP_SysCtlPeripheralEnable (SYSCTL_PERIPH_GPIOK);

MAP_SysCtlPeripheralEnable (SYSCTL_PERIPH_GPIOL);

MAP_SysCtlPeripheralEnable (SYSCTL_PERIPH_GPIOM);

MAP_SysCtlPeripheralEnable (SYSCTL_PERIPH_GPION);

MAP_SysCtlPeripheralEnable (SYSCTL_PERIPH_GPIOQ);

/*基于 HW/SW ICD 的 EPI 引脚分配*/

MAP_GPIOPinConfigure (GPIO_PH0_EPI0S0);

MAP_GPIOPinConfigure (GPIO_PH1_EPI0S1);

MAP_GPIOPinConfigure (GPIO_PH2_EPI0S2);

MAP_GPIOPinConfigure (GPIO_PH3_EPI0S3);

MAP_GPIOPinConfigure (GPIO_PC7_EPI0S4);

MAP_GPIOPinConfigure (GPIO_PC6_EPI0S5);

MAP_GPIOPinConfigure (GPIO_PC5_EPI0S6);

MAP_GPIOPinConfigure (GPIO_PC4_EPI0S7);

MAP_GPIOPinConfigure (GPIO_PA6_EPI0S8);

MAP_GPIOPinConfigure (GPIO_PA7_EPI0S9);

MAP_GPIOPinConfigure (GPIO_PG1_EPI0S10);

MAP_GPIOPinConfigure (GPIO_PG0_EPI0S11);

MAP_GPIOPinConfigure (GPIO_PM3_EPI0S12);

MAP_GPIOPinConfigure (GPIO_PM2_EPI0S13);

MAP_GPIOPinConfigure (GPIO_PM1_EPI0S14);

MAP_GPIOPinConfigure (GPIO_PM0_EPI0S15);

MAP_GPIOPinConfigure (GPIO_PL0_EPI0S16);

MAP_GPIOPinConfigure (GPIO_PL1_EPI0S17);

MAP_GPIOPinConfigure (GPIO_PL2_EPI0S18);

MAP_GPIOPinConfigure (GPIO_PL3_EPI0S19);

MAP_GPIOPinConfigure (GPIO_PQ0_EPI0S20);// PLD Memory AB15

MAP_GPIOPinConfigure (GPIO_PQ1_EPI0S21);// PLD Memory AB16

MAP_GPIOPinConfigure (GPIO_P2_EPI0S22);// PLD Memory AB17

MAP_GPIOPinConfigure (GPIO_PQ3_EPI0S23);// PLD 存储器 AB18

MAP_GPIOPinConfigure (GPIO_PK7_EPI0S24);// EPI_BSEL0n

MAP_GPIOPinConfigure (GPIO_PK6_EPI0S25);// EPI_BSEL1n

MAP_GPIOPinConfigure (GPIO_PL4_EPI0S26);// EPI_CS0n (FPGA)。 映射到地址范围0x60000000

MAP_GPIOPinConfigure (GPIO_PB2_EPI0S27);// EPI_CS1n (MRAM)。 映射到地址范围0x

MAP_GPIOPinConfigure (GPIO_PB3_EPI0S28);// EPI_RDN

MAP_GPIOPinConfigure (GPIO_PN2_EPI0S29);// EPI_WRn

MAP_GPIOPinConfigure (GPIO_PN3_EPI0S30);// EPI_ALE

//以下信号被路由到 PLD 螺母、不计划使用

MAP_GPIOPinConfigure (GPIO_PK5_EPI0S31);// EPI_CLK*

MAP_GPIOPinConfigure (GPIO_PK4_EPI0S32);// EPI_iRDY*

MAP_GPIOPinConfigure (GPIO_PL5_EPI0S33);// EPI_CS3*

MAP_GPIOPinConfigure (GPIO_PN4_EPI0S34);// EPI_CS2*

MAP_GPIOPinConfigure (GPIO_PN5_EPI0S35);// EPI_CRE*

MAP_GPIOPinTypeEPI (GPIO_PORTA_BASE、(GPIO_PIN_7 | GPIO_PIN_6));

MAP_GPIOPinTypeEPI (GPIO_PORTB_BASE、(GPIO_PIN_3 | GPIO_PIN_2));

MAP_GPIOPinTypeEPI (GPIO_PORTC_BASE (GPIO_PIN_7 | GPIO_PIN_6 | GPIO_PIN_5 | GPIO_PIN_4));

MAP_GPIOPinTypeEPI (GPIO_PORTG_BASE (GPIO_PIN_1 | GPIO_PIN_0));

MAP_GPIOPinTypeEPI (GPIO_PORth_BASE、(GPIO_PIN_3 | GPIO_PIN_2 | GPIO_PIN_1 | GPIO_PIN_0));

MAP_GPIOPinTypeEPI (GPIO_PORTK_BASE、(GPIO_PIN_7 | GPIO_PIN_6 | GPIO_PIN_5 | GPIO_PIN_4));

MAP_GPIOPinTypeEPI (GPIO_PORTL_BASE、(GPIO_PIN_5 | GPIO_PIN_4 | GPIO_PIN_3 | GPIO_PIN_2 | GPIO_PIN_1 | GPIO_PIN_0));

MAP_GPIOPinTypeEPI (GPIO_PORTM_BASE、(GPIO_PIN_3 | GPIO_PIN_2 | GPIO_PIN_1 | GPIO_PIN_0));

MAP_GPIOPinTypeEPI (GPIO_PORTN_BASE (GPIO_PIN_5 | GPIO_PIN_4 | GPIO_PIN_3 | GPIO_PIN_2));

/*启用到 EPI 的时钟并等待它准备就绪*/

MAP_SysCtlPeripheralEnable (SYSCTL_PERIPH_EPI0);

while (! (MAP_SysCtlPeripheralReady (SYSCTL_PERIPH_EPI0))

{

}

//将 EPI 配置为在120 MHz 处访问 MRAM 存储器将 EPI 时钟设置为 MRAM (120MHz)的系统时钟。

*和四分之一的系统时钟用于 FPGA(30Mhz )*/

EPIDividerSet (EPI0_BASE、3);

// EPIDividerSet (EPI0_BASE、0x00030003);//时钟速度降低30Mhz、仍然损坏

//主机总线16位接口

EPIModeSet (EPI0_BASE、EPI_MODE_HB16);

//根据 ICD 进行 HB16设置、以允许单个配置

// PLL 存储器(CS0)和 MRAM (CS1)

EPIConfigHB16Set (EPI0_BASE、

(EPI_HB16_MODE_ADMUX |

EPI_HB16_IN_READY_EN |

EPI_HB16_BSEL |

EPI_HB16_CSCFG_ALE_DUAL_CS |

EPI_HB16_CSBAUD)、

8);// PF 为0

//配置 CS0、FPGA 接口、请参阅 ICD、FPGA Works

EPIConfigHB16CSSet (EPI0_BASE、0、

(EPI_HB16_MODE_ADMUX |

EPI_HB16_WRWAIT_0 |

EPI_HB16_RDWAIT_0 |

EPI_HB16_ALE_HIGH);

//配置 CS1、MRAM 接口、请参阅 ICD

EPIConfigHB16CSSet (EPI0_BASE、1、

(EPI_HB16_MODE_ADMUX |

EPI_HB16_WRWAIT_1 |

EPI_HB16_RDWAIT_1 |

EPI_HB16_ALE_HIGH);

EPIAddressMapSet (EPI0_BASE、((EPI_ADDR_RAM_BASE_6 | EPI_ADDR_RAM_SIZE_16MB)|(EPI_ADDR_PER_BASE_A | EPI_ADDR_PER_SIZE_16MB));

/***调整 MRAM 等待状态、将读取和写入都减少1个等待状态****

//EPIConfigHB16TimingSet (EPI0_BASE、1、(EPI_HB16_RDWAIT_MINUS_ENABLE | EPI_HB16_WRWAIT_MINUS_ENABLE));

//EPIConfigHB16TimingSet (EPI0_BASE、1、EPI_HB16_RDWAIT_MINUS_ENABLE);

//EPIConfigHB16TimingSet (EPI0_BASE、1、EPI_HB16_WRWAIT_MINUS_ENABLE);

/*通过轮询等待唤醒完成

*初始化序列位。 当 SDRAM 接口时该位为真

*会执行初始化、而 SDRAM 接口时为 false

*它不是在一个唤醒期间。 */

while (EPI0->STAT 和 EPI_STAT_INITSEQ)

{

}

退货(状态);

}

提前感谢。

Perry