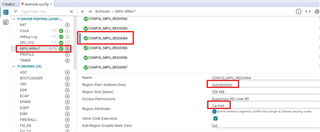

主题中讨论的其他器件:SysConfig

工具与软件:

尊敬的 TI 专家:

(FPGA 套件): https://www.arrow.com/en/products/dk-dev-10cx220-a/intel?q=DK-DEV-10CX220-A

我尝试使用此 FPGA 套件作为 EP、使用234EVM 作为 RC。

EP 具有两个 bar、即 bar0和 bar1。

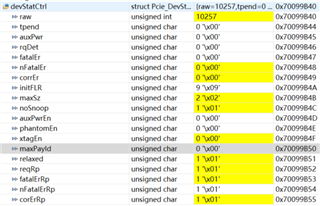

我可以从 EP 读取 status_cmd、但无法为 EP 配置 bar。 下面是我的代码。

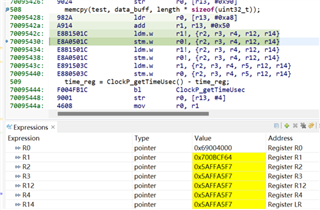

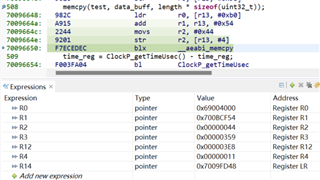

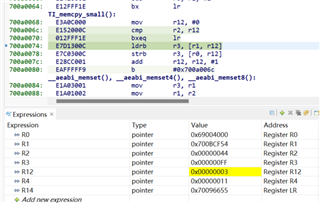

它总是停留在: type0BarIdx.idx 读在 PCIe_cfgBar()中。

我的 SDK 版本:mcu_plus_sdk_am243x_09_00_00_35

请帮我解决这个问题!

谢谢

Chunyang

int32_t PCIe_FPGA_EP_TEST (Pcie_Handle 句柄)

{

int32_t status = SystemP_Success;

Pcie_Registers getRegs;

Pcie_Status CmdReg 状态命令;

memset (&getRegs、0、sizeof (getRegs));

getRegs.statusCmd =&statusCmd;

status = PCIe_readRegs (handle、PCIe_location_remote、&getRegs);

if (SYSTEMP_SUCCESS!= STATUS)

{

DebugP_LOG ("FPGA 状态读取测试失败\r\n");

}

设计

{

DebugP_LOG ("FPGA 状态读取测试完成\r\n");

}

返回状态;

}

int32_t PCIe_fpga_ep_bar1_cfg (Pcie_Handle 句柄)

{

int32_t status = SystemP_Success;

Pcie_Bar 配置 barCfg;

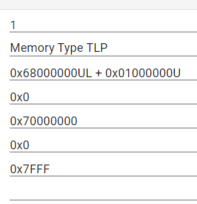

barCfg.location = PCIe_location_remote;

barCfg.mode = PCIe_EP_MODE;

barCfg.base = 0x70000000;

barCfg.prefetch = PCIe_bar_non_pref;

barCfg.type = PCIe_bar_TYPE32;

barCfg.memSpace = PCIe_bar_MEM_MEM;

barCfg.idx = 0;//1;

status = PCIe_cfgBar (handle、&barCfg);

//DebugP_assert (SystemP_SUCCESS == status);

if (SYSTEMP_SUCCESS!= STATUS)

{

DebugP_log ("FPGA bar1 configure fail\r\n");

}

设计

{

DebugP_LOG ("FPGA bar1 configure done\r\n");

}

返回状态;

}