主题中讨论的其他器件: SysConfig

工具与软件:

您好、专家。

我们希望使用 DDR 保存复位期间保留的一些变量。 我们测试过它在默认情况下可以正常工作、但存在两个问题。

1) 1) DDR 的前16个字节将成为固定数据(00 FF 00 FF 00 FF 00 FF 00 FF)

2) 2)如果 DDR 未在复位后立即初始化、但在几秒钟后初始化、则 DDR 中的数据将部分异常。

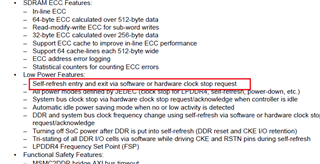

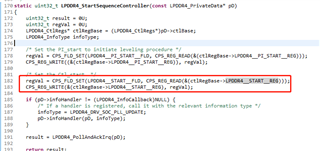

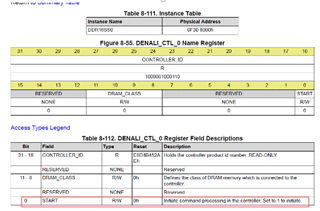

因此、我们要使用 TRM 支持的 DDR 自刷新模式。 但我们在 TRM 中没有看到任何用于设置 SRE/SRX 命令的寄存器、也没有在 SDK 中看到相关函数。 您能否帮助了解如何通过 AM243X 进入和退出自刷新? 如何 实现软件、以及如何实现硬件?