Thread 中讨论的其他器件:TIDEP-01032、

工具与软件:

尊敬的 TI 专家:

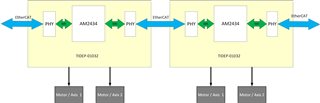

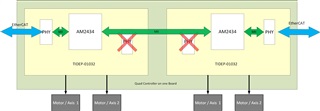

我们希望将两个 TIDEP-01032双电机控制器组合在一块板上、以构建一个四轴控制器。

为此、我们需要通过 EtherCAT 连接两个 Sitara AM2434、使它们每个都作为单独的 EtherCAT 节点运行。

由于在一个电路板上发生该情况、我们希望省略两个 Sitaras 之间的 PHY 并背对背连接 RGMII。

1)对于如何做到这一点、是否有任何建议?

2) 2) TIDEP-01032 PRU-ICSS EtherCAT 固件能否配置为使用 MII 而不是 RGMII?

3) 3)是否有关于如何使用 MII (而不是 RGMII)实现背对背配置的建议? 一个潜在的难题是 TXC/RXC 信号、因为在 MII 中两个信号都是 PHY 的输出。

4) 4)能否 将固件配置为在一个端口上运行 MII、在第二个端口上运行 RGMII?

谢谢你

克劳斯