主题中讨论的其他器件:HALCOGEN、 TMS570LC4357

工具与软件:

您好!

我使用的是 TMS570LS3137ZWT 器件。

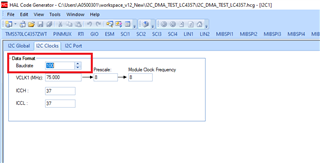

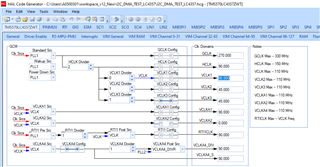

我已经将 VCLK 设置为90MHz

我已将 I2C 预分频器配置为8、以获得10MHz 的模块频率。

按照数据表公式、要获得400kHz I2C 总线、我应该将 CLKH 配置为7、将 CLKL 配置为8

然而、为了获得400kHz 频率、我必须将 CLKH 配置为4、将 CLKL 配置为4...曲折的 VCLK 频率。

我可以通过 ECLK 检查 VCLK:ECLK = VCLK/900给了我一个非常棒的100kHz 方波信号...

我对这种配置感到困惑...

您能帮助我理解吗?

提前感谢您。

Francois