主题中讨论的其他器件: SysConfig

工具与软件:

大家好:

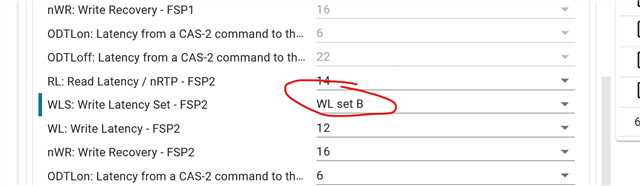

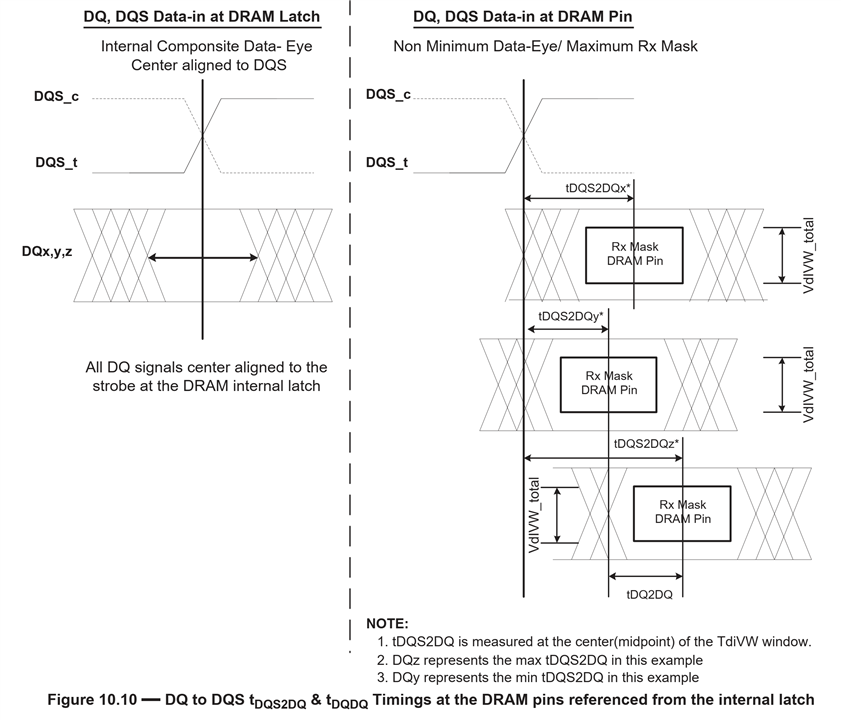

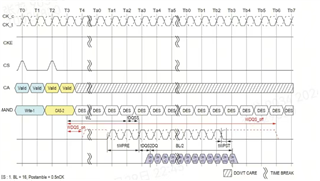

我们的项目使用带有 LPDDR4外部 RAM 模型 IS43LQ32256B-062BLI&ISSI 的 AM2432。 最近、在测试 DDR 时序期间、我们发现当 SOC 写入 DDR 时、DQS 和 DQ 之间的相位关系不符合 DDR 手册。 您能否帮助我们检查是否可以通过 DDR 配置解决该问题。

注意:

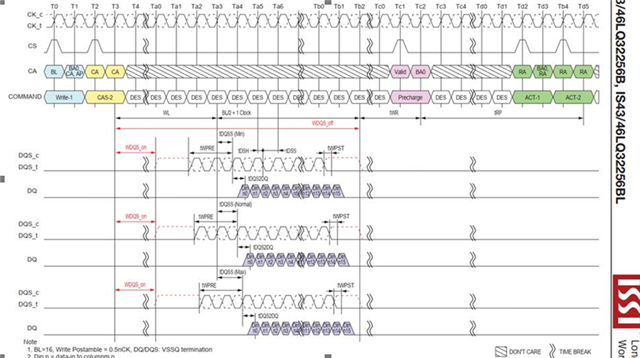

图1显示了 LPDDR4写入操作的时序

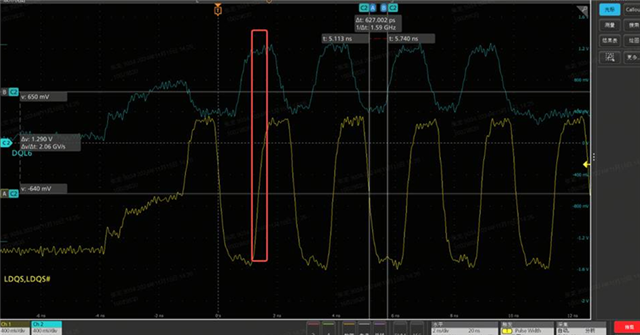

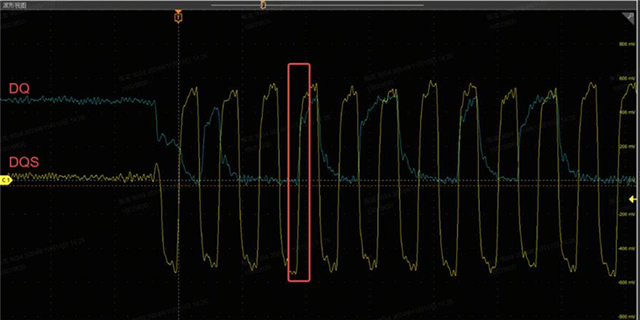

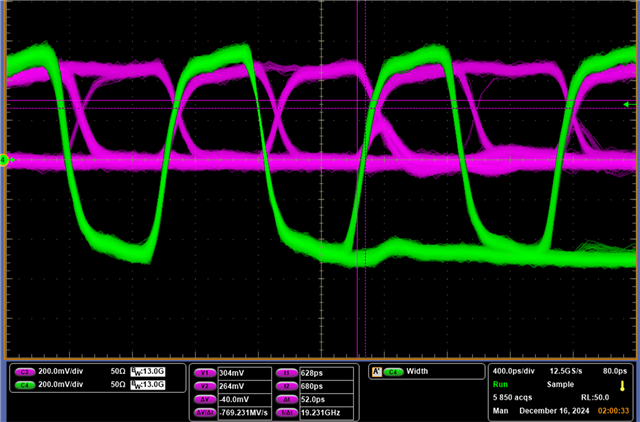

图2显示了我们测试的波形

图1显示了 LPDDR4写入操作的时序

图2显示了我们测试的波形