工具与软件:

您好!

如果未遵循 NDA、您能否在 TMS570 TRM (SPNU563A–2018年3月、第144页)中解释以下注释背后的原理?

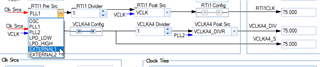

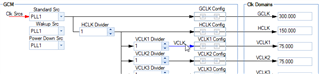

"注:选择一个非 VCLK 的 RTICLK1时钟源时、当应用为非 VCLK 的 RTICLK1域选择一个时钟源时、应用必须确保产生的 RTICLK1频率小于或等于 VCLK 频率除以3。 该应用可以配置 RCLKSRC 寄存器的 RTI1DIV 字段以将所选时钟源频率除以1、2、4或8来满足该要求。"

具体而言、达到该要求的原因是什么、如果 RTI 时钟频率设置为大于 VCLK 频率除以3、则可能会发生什么情况?

谢谢你。