工具与软件:

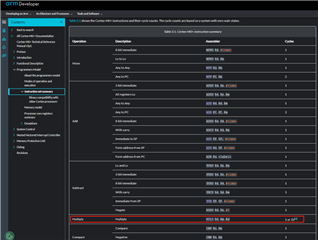

例如、我们可以看到 CPU 通过占用4个时钟周期来执行指令 MULS。 但来自 ARM 网站的信息表明它需要1或32个时钟周期。 请帮助 comfirm。

https://developer.arm.com/documentation/ddi0484/c/Programrs-Model/Instruction-set-summary

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

例如、我们可以看到 CPU 通过占用4个时钟周期来执行指令 MULS。 但来自 ARM 网站的信息表明它需要1或32个时钟周期。 请帮助 comfirm。

https://developer.arm.com/documentation/ddi0484/c/Programrs-Model/Instruction-set-summary

尊敬的 Peter:

因此、每条指令等待状态似乎需要2个 CPU 时钟周期、我是对吗?[/quot]正确。 它将再花2个 CPU 时钟来等待闪存。

MULS 指令理论上总共需要3个 CPU 时钟周期、但实际上需要4个 CPU 时钟周期。首先、我们不对此进行基准测试、因此我无法判断该测试结果是否符合预期。 [我也认为 CPU 时钟=3更合理、但我不能保证这一点。]

其次、我不确定是如何对其进行基准测试的、MSPM0器件确实具有闪存预取/缓存。 因此、您的测试可能不准确。

我可以推荐她的测试方法:

将 汇编代码设定到 SRAM 中、并在 SRAM 中运行来查看 CPU 时钟消耗是否为1。 当在 SRAM 中运行时、它应该为零等待状态。

B.R.

SAL

[/quote]

你好、 Peter

在调试启动和停止期间、调试器会向 M0+内核插入一些指令。

这可能需要一些周期。

即使调试某些单周期指令、结果也可能是4个 SysTick 周期。

运行20次 mul、SysTick 向下计数26次。

运行10次 mul、SysTick 向下计数16次。

运行5次 mul、SysTick 向下计数11次。

对于多路复用步骤调试、根据该测试结果、它将需要额外的6个 SysTick 周期。

我想对于单步调试、它将需要额外的3个 SysTick 周期。

下面是测试演示:

e2e.ti.com/.../Instruction_5F00_MUL_5F00_Test_5F00_CycleTest_5F00_G3507.zip

希望本指南能为您提供帮助。

此致、

Helic

尊敬的 Helic:

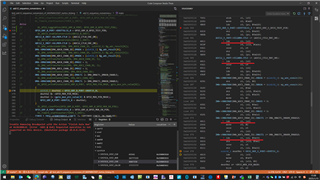

感谢您的解释。 对我来说很有帮助。 我通过单步调试检查我的代码、发现几乎所有指令时钟周期(执行额外的3个时钟周期)都符合来自 ARM 网站的信息、但只有 LDR 指令。 LDR 指令有时可能需要3或5个时钟周期、正如下面的屏幕截图中用红色标记的那样。

下面是我的测试代码、请帮助我们弄清楚它。

e2e.ti.com/.../instructions_5F00_test_5F00_demo.zip

谢谢!

你好、 Peter

LDR 指令有时可能需要3或5个时钟周期、正如我在下面的屏幕截图中以红色标记的那样。

这是正常的、因为恢复+断点和单步调试都需要向 CPU 插入一些额外指令。

此致、

Helic

尊敬的 Helic:

即使我在没有调试器的情况下运行代码、LDR 指令有时仍需要3个 ro 5个周期。 这里是我修改后的测试代码。

e2e.ti.com/.../instructions_5F00_test_5F00_demo_5F00_20250116.zip

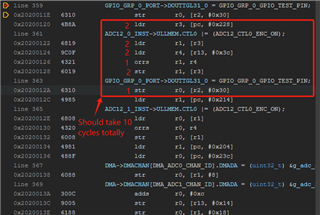

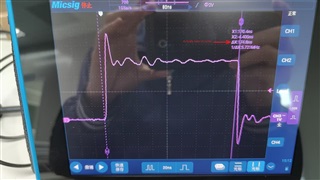

在此代码中、我 在361行中添加 DL_GPIO_togglePins 之前和之后的 DL_ADC12_enableConversions、然后 在不使用调试器的情况下运行代码。 正脉冲持续时间为162.5或175ns、等于13或14个周期。 但是、预期周期数为10。 根据昨天的测试结果、我认为额外的3或4个周期是由指令 LDR R1、[R3]进行的。

尊敬的 Peter:

我做了一些测试。 LDR 指令确实具有不同的操作周期。

-[LDR Rd,...] LDR 指令将把操作值返回 Rd 寄存器。

当访问不同的外设寄存器时、返回外设寄存器值需要花费几个额外的 CPU 周期。

在我的测试中、 对于 GPIO 模块、LDR 指令将花费2个周期1个周期[更新];对于 ADC0模块、LDR 指令将花费5个周期;对于 SPI0模块、LDR 指令将花费3个周期。

我怀疑以下内容:

当 CPU 访问外设寄存器时、可能有时钟同步行为使操作正常、这会导致额外的 CPU 周期。

B.R.

SAL