Other Parts Discussed in Thread: MSP432E401Y

工具与软件:

尊敬的 TI:

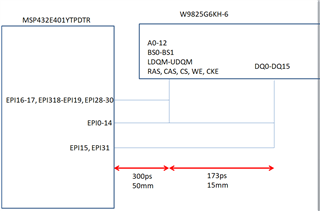

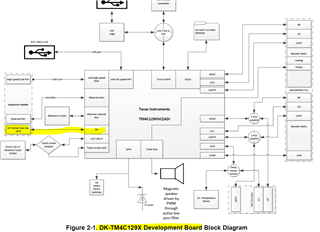

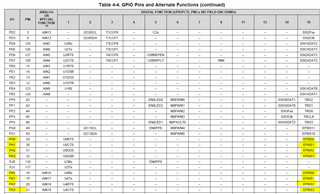

我需要通过 EPI 接口将 SDRAM 存储器连接到 MSP432E401Y、

1-)可以使用 W9825G6KH-6存储器吗? 它是否与 EPI 接口兼容?

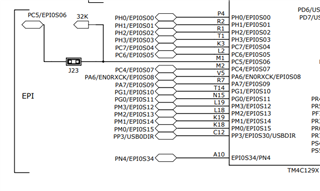

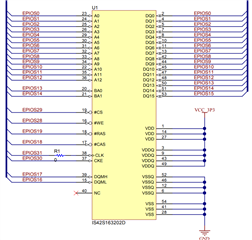

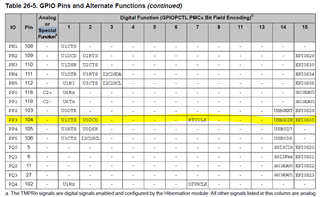

2-)我附加 SDRAM 存储器和 MSP432E401Y 之间的连接图。 随附的原理图是否正确? 请注意、EPI0S0-12由地址总线和数据总线共用、而 EPI0S13-14由数据总线和存储体选择共用。 是这样吗?

3-)原理图是否需要终端电阻器或其他元件(我仅指与存储器相关的器件)?

非常感谢。 此致。