https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1502320/tlv320aic3104-unable-to-setup-pll

器件型号:TLV320AIC3104工具/软件:

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1502320/tlv320aic3104-unable-to-setup-pll

器件型号:TLV320AIC3104工具/软件:

我在这里下载了驱动程序文件: www.ti.com.cn/.../TLV320AIC31XX-DRIVERS。

DTS:

i2c_4{

- clock-frequency = <400000>;

+ clock-frequency = <100000>;

}

+ tlv320aic3x: tlv320aic3x@1b {

+ #sound-dai-cells = <1>;

+ compatible = "ti,tlv320aic3x";

+ reg = <0x1b>;

+ reset-gpios = <&peri_port0 23 GPIO_ACTIVE_LOW>;

+ AVDD-supply = <&tlv3v3_fixed>;

+ IOVDD-supply = <&tlv1v8_fixed>;

+ DRVDD-supply = <&tlv3v3_fixed>;

+ DVDD-supply = <&tlv1v8_fixed>;

+ };

通过日志、我发现 aic3x->sysclk aic3x_hw_params() 函数中的值为0。

它是 ALSA 架构。 在 DTS 中、的配置 mclk_set 为 <24576000>。

snd2_tlv:snd2_tlv {

状态="正常";

Model ="s100snd2-tlv320";

compatible ="hobot, s100-snd-AC-FDX-MASTER";

I2S_MODE =<1>;/*1:I2S 模式;7:DSP_A 模式*/

WORK_MODE =<1>;/*0:半双工;1:全双工*/

channel_max =<2>;

MCLK_SET =<24576000>;

Dai-link@0{

DI-format ="I2S_";//"I2S"/"DSP_A"

链接名称="j6dailink0";

CPU{

sound-dai =<&i2s0 0>;

};

编解码器{

sound-dai =<&tlv320aic3x 0>;

};

};

Dai-link@1{

DAI-FORMAT ="I2S_";

链接名称="j6dailink1";

CPU{

sound-dai =<&i2s0 1>;

};

编解码器{

sound-dai =<&tlv320aic3x 0>;

};

};

};

您好、

是的、抱歉- aic3x.c 是正确的驱动程序。 我假设您的 FS 是48K? 您仍然需要启用 PLL 来生成内部时钟、驱动程序似乎应该 被 DTS 文件告知 fsref、可能还有 MCLK 速率。 您是否 在 MCLK 引脚上提供24576000Hz 时钟、并且是否提供48K WCLK 和 BCLK?

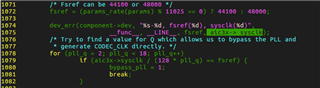

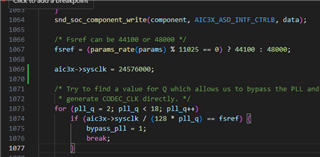

您可能需要在驱动程序代码本身中设置 SYSCLK、如下所示:

好极了

Mir