https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1506460/tac5242-clocking-question

器件型号:TAC5242工具/软件:

您好:

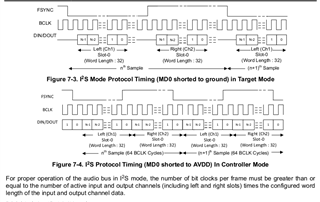

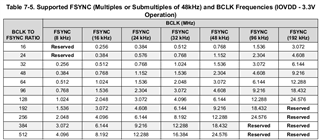

我希望使用字长为32b 且采样率为192k 的 I2S 接口在目标模式下运行 TAC5242。 为了满足 I2S 接口的要求、这意味着由于不使用第一个 BCLK、因此我必须使用大于64的 BCLK 与 FSYNC 的比率。 这意味着我必须根据表7-5生成18.432MHz 的 BCLK (如下所示)。 无法使18.432时钟完美无缺会造成什么后果? 如果我偏离100ppm、这是否是个问题? 即使绝对 FSYNC 和 BCLK 频率关闭、BCLK 与 FSYNC 的比率仍然是96、是否正常?

感谢您的高级帮助。