工具/软件:

尊敬的 TI 团队:

使用 tinyplay 播放 WAV 文件时没有声音。

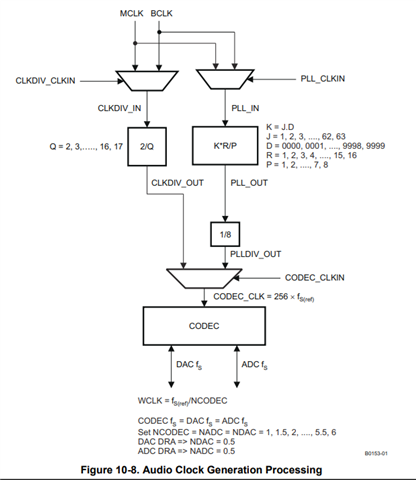

编解码器 DIN 上有一个数据信号。 MCLK 的频率为11.36 MHz、BCLK 的频率为14.14 MHz。

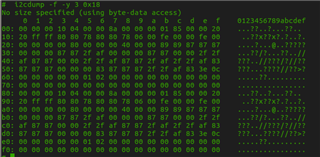

i2cdump 信息如下所示:

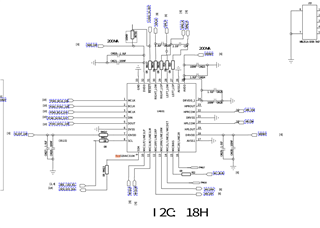

tinymix 配置:

Number of controls: 114 ctl type num name device value 0 INT 1 Left Line Mixer Line2R Bypass Volume 0118 (range 0->118) 1 INT 1 Right Line Mixer Line2L Bypass Volume 0111 (range 0->118) 2 INT 1 Left HP Mixer Line2R Bypass Volume 0118 (range 0->118) 3 INT 1 Right HP Mixer Line2L Bypass Volume 0111 (range 0->118) 4 INT 1 Left HPCOM Mixer Line2R Bypass Volume 0118 (range 0->118) 5 INT 1 Right HPCOM Mixer Line2L Bypass Volume 0111 (range 0->118) 6 INT 2 Line Line2 Bypass Volume 0111, 71 (range 0->118) 7 INT 2 HP Line2 Bypass Volume 0111, 71 (range 0->118) 8 INT 2 HPCOM Line2 Bypass Volume 0111, 71 (range 0->118) 9 INT 2 Mono Line2 Bypass Volume 0111, 71 (range 0->118) 10 INT 2 Mono PGA Bypass Volume 071, 71 (range 0->118) 11 INT 2 Mono DAC Playback Volume 071, 71 (range 0->118) 12 BOOL 1 Mono Playback Switch 0Off 13 INT 1 Mono Playback Volume 08 (range 0->9) 14 INT 2 PCM Playback Volume 0118, 118 (range 0->127) 15 INT 1 Left Line Mixer PGAR Bypass Volume 0118 (range 0->118) 16 INT 1 Left Line Mixer DACR1 Playback Volume 0118 (range 0->118) 17 INT 1 Right Line Mixer PGAL Bypass Volume 0111 (range 0->118) 18 INT 1 Right Line Mixer DACL1 Playback Volume 0111 (range 0->118) 19 INT 1 Left HP Mixer PGAR Bypass Volume 0118 (range 0->118) 20 INT 1 Left HP Mixer DACR1 Playback Volume 0118 (range 0->118) 21 INT 1 Right HP Mixer PGAL Bypass Volume 0118 (range 0->118) 22 INT 1 Right HP Mixer DACL1 Playback Volume 0118 (range 0->118) 23 INT 1 Left HPCOM Mixer PGAR Bypass Volume 0118 (range 0->118) 24 INT 1 Left HPCOM Mixer DACR1 Playback Volume 0118 (range 0->118) 25 INT 1 Right HPCOM Mixer PGAL Bypass Volume 0118 (range 0->118) 26 INT 1 Right HPCOM Mixer DACL1 Playback Volume 0118 (range 0->118) 27 INT 2 Line PGA Bypass Volume 0111, 71 (range 0->118) 28 INT 2 Line DAC Playback Volume 0111, 71 (range 0->118) 29 INT 2 HP PGA Bypass Volume 0111, 71 (range 0->118) 30 INT 2 HP DAC Playback Volume 0111, 71 (range 0->118) 31 INT 2 HPCOM PGA Bypass Volume 071, 71 (range 0->118) 32 INT 2 HPCOM DAC Playback Volume 071, 71 (range 0->118) 33 INT 2 Line Playback Volume 08, 8 (range 0->9) 34 BOOL 2 Line Playback Switch 0Off, Off 35 INT 2 HP Playback Volume 08, 8 (range 0->9) 36 BOOL 2 HP Playback Switch 0Off, Off 37 INT 2 HPCOM Playback Volume 08, 8 (range 0->9) 38 BOOL 2 HPCOM Playback Switch 0Off, Off 39 BOOL 2 AGC Switch 0Off, Off 40 ENUM 1 Left AGC Target level 0> -5.5dB, -8dB, -10dB, -12dB, -14dB, -17dB, -20dB, -24dB, 41 ENUM 1 Right AGC Target level 0> -5.5dB, -8dB, -10dB, -12dB, -14dB, -17dB, -20dB, -24dB, 42 ENUM 1 Left AGC Attack time 0> 8ms, 11ms, 16ms, 20ms, 43 ENUM 1 Right AGC Attack time 0> 8ms, 11ms, 16ms, 20ms, 44 ENUM 1 Left AGC Decay time 0> 100ms, 200ms, 400ms, 500ms, 45 ENUM 1 Right AGC Decay time 0> 100ms, 200ms, 400ms, 500ms, 46 BOOL 2 De-emphasis Switch 0On, On 47 INT 2 PGA Capture Volume 032, 32 (range 0->119) 48 BOOL 2 PGA Capture Switch 0On, On 49 ENUM 2 ADC HPF Cut-off 0Disabled, 0.0045xFs, > 0.0125xFs, 0.025xFs, , Disabled, 0.0045xFs, > 0.0125xFs, 0.025xFs, 50 ENUM 1 Output Driver Power-On time 0> 0us, 10us, 100us, 1ms, 10ms, 50ms, 100ms, 200ms, 400ms, 800ms, 2s, 4s, 51 ENUM 1 Output Driver Ramp-up step 0> 0ms, 1ms, 2ms, 4ms, 52 ENUM 1 Left DAC Mux 0> DAC_L1, DAC_L3, DAC_L2, 53 ENUM 1 Left HPCOM Mux 0> differential of HPLOUT, constant VCM, single-ended, 54 ENUM 1 Right DAC Mux 0> DAC_R1, DAC_R3, DAC_R2, 55 ENUM 1 Right HPCOM Mux 0> differential of HPROUT, constant VCM, single-ended, differential of HPLCOM, external feedback, 56 ENUM 1 Left Line1L Mux 0single-ended, > differential, 57 ENUM 1 Left Line1R Mux 0> single-ended, differential, 58 ENUM 1 Right Line1L Mux 0> single-ended, differential, 59 ENUM 1 Right Line1R Mux 0single-ended, > differential, 60 BOOL 1 Left PGA Mixer Line1L Switch 0On 61 BOOL 1 Left PGA Mixer Line1R Switch 0Off 62 BOOL 1 Left PGA Mixer Line2L Switch 0On 63 BOOL 1 Left PGA Mixer Mic3L Switch 0Off 64 BOOL 1 Left PGA Mixer Mic3R Switch 0Off 65 ENUM 1 Left Line2L Mux 0single-ended, > differential, 66 BOOL 1 Right PGA Mixer Line1R Switch 0On 67 BOOL 1 Right PGA Mixer Line1L Switch 0Off 68 BOOL 1 Right PGA Mixer Line2R Switch 0On 69 BOOL 1 Right PGA Mixer Mic3L Switch 0Off 70 BOOL 1 Right PGA Mixer Mic3R Switch 0Off 71 ENUM 1 Right Line2R Mux 0single-ended, > differential, 72 BOOL 1 Left Line Mixer PGAL Bypass Switch 0On 73 BOOL 1 Left Line Mixer DACL1 Switch 0On 74 BOOL 1 Left Line Mixer PGAR Bypass Switch 0Off 75 BOOL 1 Left Line Mixer DACR1 Switch 0Off 76 BOOL 1 Left Line Mixer Line2L Bypass Switch 0On 77 BOOL 1 Left Line Mixer Line2R Bypass Switch 0Off 78 BOOL 1 Right Line Mixer PGAL Bypass Switch 0On 79 BOOL 1 Right Line Mixer DACL1 Switch 0On 80 BOOL 1 Right Line Mixer PGAR Bypass Switch 0Off 81 BOOL 1 Right Line Mixer DACR1 Switch 0On 82 BOOL 1 Right Line Mixer Line2L Bypass Switch 0On 83 BOOL 1 Right Line Mixer Line2R Bypass Switch 0Off 84 BOOL 1 Left HP Mixer PGAL Bypass Switch 0On 85 BOOL 1 Left HP Mixer DACL1 Switch 0On 86 BOOL 1 Left HP Mixer PGAR Bypass Switch 0Off 87 BOOL 1 Left HP Mixer DACR1 Switch 0Off 88 BOOL 1 Left HP Mixer Line2L Bypass Switch 0On 89 BOOL 1 Left HP Mixer Line2R Bypass Switch 0Off 90 BOOL 1 Right HP Mixer PGAL Bypass Switch 0Off 91 BOOL 1 Right HP Mixer DACL1 Switch 0Off 92 BOOL 1 Right HP Mixer PGAR Bypass Switch 0Off 93 BOOL 1 Right HP Mixer DACR1 Switch 0On 94 BOOL 1 Right HP Mixer Line2L Bypass Switch 0On 95 BOOL 1 Right HP Mixer Line2R Bypass Switch 0Off 96 BOOL 1 Left HPCOM Mixer PGAL Bypass Switch 0Off 97 BOOL 1 Left HPCOM Mixer DACL1 Switch 0On 98 BOOL 1 Left HPCOM Mixer PGAR Bypass Switch 0Off 99 BOOL 1 Left HPCOM Mixer DACR1 Switch 0Off 100 BOOL 1 Left HPCOM Mixer Line2L Bypass Switch 0On 101 BOOL 1 Left HPCOM Mixer Line2R Bypass Switch 0Off 102 BOOL 1 Right HPCOM Mixer PGAL Bypass Switch 0Off 103 BOOL 1 Right HPCOM Mixer DACL1 Switch 0Off 104 BOOL 1 Right HPCOM Mixer PGAR Bypass Switch 0Off 105 BOOL 1 Right HPCOM Mixer DACR1 Switch 0On 106 BOOL 1 Right HPCOM Mixer Line2L Bypass Switch 0On 107 BOOL 1 Right HPCOM Mixer Line2R Bypass Switch 0Off 108 BOOL 1 Mono Mixer Line2L Bypass Switch 0On 109 BOOL 1 Mono Mixer PGAL Bypass Switch 0Off 110 BOOL 1 Mono Mixer DACL1 Switch 0On 111 BOOL 1 Mono Mixer Line2R Bypass Switch 0Off 112 BOOL 1 Mono Mixer PGAR Bypass Switch 0Off 113 BOOL 1 Mono Mixer DACR1 Switch 0On