工具/软件:

您好的团队、

我想仔细检查以下几点。

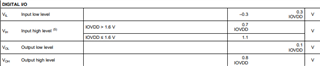

1:测量 tr 和 tf 时是否需要这些电压?

2: 数字 I/O 参数的最小/最大电压是否也适用于 MCLK?

此致、

Yu

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好的团队、

我想仔细检查以下几点。

1:测量 tr 和 tf 时是否需要这些电压?

2: 数字 I/O 参数的最小/最大电压是否也适用于 MCLK?

此致、

Yu

您好、Jeff San、

很抱歉、我忘了提及、但我说的是 MCLK;

[报价 userid="603570" url="~/support/audio-group/audio/f/audio-forum/1517275/tlv320aic3101-rise-fall-time-measurement-and-mclk-requirements/5838575 #5838575"]对交流分量(例如上升/下降时间和 H/L 长度)的要求[/报价]表9.6显示了 BCLK 及其他时的时序特性、但不显示 MCLK。 主模式详细信息是否适用于 MCLK?

/

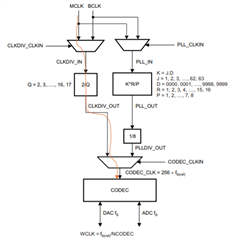

此外、在禁用24.576MHz 的情况下、MCLK=PLL、FS=48kHz 时的时钟树设置是否正确? Q= 4设置存在音频间歇性中断且 Q=2本底噪声高的问题。

MCLK=MCLK 24.576MHz

Q=4

12.288MHz

FS=CODEC_CLK/256=48kHz

BR、

Yu

你好佐藤山、

假设在从模式下不使用 MCLK、但如果您在从模式下使用 MCLK、则可以参阅 MCLK 的主模式详细信息。

是 Q=4正确。 Q = 2将创建内部96kHz 采样、这将与48kHz I2S 时钟冲突并产生问题。

间歇性切断可能不是时钟分频器问题。 这通常是由时钟错误或数据上的噪声导致数据接收器失去锁存引起的。 您还可以仔细检查我们上面讨论的时序要求。 您讨论的是 ADC 数据切断还是模拟输出音频切断?

此致、

Jeff McPherson

您好、Jeff San、

假设从模式下不使用 MCLK、但如果您在从模式下使用 MCLK、则可以参阅 MCLK 的主模式详细信息。

虽然没有假定、但 MCLK 仍然可以在从模式下使用?

该系统用于将3个 TLV320AIC3101同步在一起、并更大限度地减少时钟时序差异的差异。 您是否建议使用 BCLK 并通过每个器件的 PLL 生成所有内部时钟、而不是在所有3个器件上以菊花链形式连接 MCLK?

您讨论的是 ADC 数据切断还是模拟输出音频切断?

我来检查一下。

BR、

Yu

您好、Jeff San、

您讨论的是 ADC 数据切断还是模拟输出音频切断?

这是 ADC 数据切断。

我是否可以向您提供任何其他信息来查找问题的原因? (可能是时钟信号?)

BR、

Yu

你好佐藤山、

ADC 数据下降通常是由时钟上的噪声或频率不正确引起的。 我建议客户仔细检查时序要求、确保信号上没有明显的噪音。

此外、如果他们已经连接三个器件、则一次尝试仅测试一个编解码器、以查看一个器件上的 ADC 数据是否稳定。 将多个器件连接到同一个时钟会引入反射错误、从而需要使用端接电阻器来解决。 如果时钟在转换边沿有锯齿状边沿、则在示波器上可以看到反射

此致、

Jeff McPherson

您好、Jeff San、

我懂了。 谢谢!

如果问题没有解决、是否可以使用 BCLK 中的 PLL 信号作为所有3个器件的时钟源? (令人担忧的是不同延迟之间 PLL 精度的自然差异)

要将所有设备同步在一起、我建议使用从模式。 MCLK 可用作内部时钟源(如果可用)、但 BCLK 可用于。

我假设只要3个器件都同步、就会是。

BR、

Yu