工具/软件:

我将 TLV320ADC5140 连接到 STM32H750 开发板。

我在 STM32 上针对 16 位音频、4 个输出插槽和 16kHz 采样率配置了串行音频外设。

TLV320ADC5140 配置为 4 个单端输入通道、在 16 位 TDM 模式下输出 4 个时隙 — 该器件作为从器件运行。

遗憾的是、TLV320ADC5140 未在 ASI 总线上检测到采样率以及 BCLK 与 FSYNC 的比率、仅报告两者的错误。

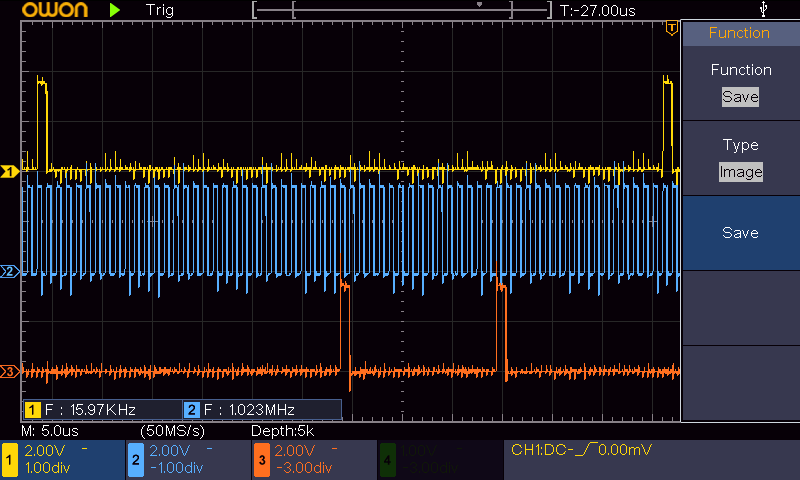

以下是串行总线的示波器轨迹:

黄色迹线为 FSYNC、蓝色为 BCLK、橙色为数据。 从频率测量中可以看出、FSYNC 为 16kHz、BCLK 为 1.024MHz、FSYNC 脉冲之间有 64 个 BCLK 周期。

下面是串行音频总线初始化后 TLV320ADC5140 寄存器的转储文件:

10:38:19.575 ->[0x02] SLEEP_CFG =*0x81 [0x00]

10:38:19.575 ->[0x05] SHDN_CFG = 0x05 [0x05]

10:38:19.575 ->[0x07] ASI_CFG0 =*0x00 [0x30]

10:38:19.575 ->[0x08] ASI_CFG1 = 0x00 [0x00]

10:38:19.575 ->[0x09] ASI_CFG2 = 0x00 [0x00]

10:38:19.575 ->[0x0B] ASI_CH1 = 0x00 [0x00]

10:38:19.575 ->[0x0C] ASI_CH2 = 0x01 [0x01]

10:38:19.575 ->[0x0D] ASI_CH3 = 0x02 [0x02]

10:38:19.575 ->[0x0E] ASI_CH4 = 0x03 [0x03]

10:38:19.575 ->[0x0F] ASI_CH5 = 0x04 [0x04]

10:38:19.575 ->[0x10] ASI_CH6 = 0x05 [0x05]

10:38:19.575 ->[0x11] ASI_CH7 = 0x06 [0x06]

10:38:19.575 ->[0x12] ASI_CH8 = 0x07 [0x07]

10:38:19.575 ->[0x13] MST_CFG0 = 0x02 [0x02]

10:38:19.575 ->[0x14] MST_CFG1 = 0x48 [0x48]

10:38:19.575 ->[0x15] ASI_STS = 0xFF [0xFF]

10:38:19.575 ->[0x16] CLK_SRC = 0x10 [0x10]

10:38:19.575 ->[0x1F] PDMCLK_CFG = 0x40 [0x40]

10:38:19.575 ->[0x20] PDMIN_CFG = 0x00 [0x00]

10:38:19.575 ->[0x21] GPIO_CFG0 = 0x22 [0x22]

10:38:19.575 ->[0x22] GPO_CFG0 = 0x00 [0x00]

10:38:19.575 ->[0x23] GPO_CFG1 = 0x00 [0x00]

10:38:19.575 ->[0x24] GPO_CFG2 = 0x00 [0x00]

10:38:19.575 ->[0x25] GPO_CFG3 = 0x00 [0x00]

10:38:19.575 ->[0x29] GPO_VAL = 0x00 [0x00]

10:38:19.575 ->[0x2A] GPIO_MON = 0x00 [0x00]

10:38:19.575 ->[0x2B] GPI_CFG0 = 0x00 [0x00]

10:38:19.575 ->[0x2C] GPI_CFG1 = 0x00 [0x00]

10:38:19.575 ->[0x2F] GPI_MON = 0x00 [0x00]

10:38:19.575 ->[0x32] INT_CFG = 0x00 [0x00]

10:38:19.575 ->[0x33] INT_MASK0 = 0xFF [0xFF]

10:38:19.575 ->[0x36] INT_LTCH0 =*0x40 [0x00]

10:38:19.575 ->[0x3B] BIAS_CFG = 0x00 [0x00]

10:38:19.575 ->[0x3C] CH1_CFG0 =*0x20 [0x00]

10:38:19.575 ->[0x3D] CH1_CFG1 = 0x00 [0x00]

10:38:19.575 ->[0x3E] CH1_CFG2 = 0xC9 [0xC9]

10:38:19.575 ->[0x3F] CH1_CFG3 = 0x80 [0x80]

10:38:19.575 ->[0x40] CH1_CFG4 = 0x00 [0x00]

10:38:19.575 ->[0x41] CH2_CFG0 =*0x20 [0x00]

10:38:19.575 ->[0x42] CH2_CFG1 = 0x00 [0x00]

10:38:19.575 ->[0x43] CH2_CFG2 = 0xC9 [0xC9]

10:38:19.575 ->[0x44] CH2_CFG3 = 0x80 [0x80]

10:38:19.575 ->[0x45] CH2_CFG4 = 0x00 [0x00]

10:38:19.575 ->[0x46] CH3_CFG0 =*0x20 [0x00]

10:38:19.575 ->[0x47] CH3_CFG1 = 0x00 [0x00]

10:38:19.575 ->[0x48] CH3_CFG2 = 0xC9 [0xC9]

10:38:19.575 ->[0x49] CH3_CFG3 = 0x80 [0x80]

10:38:19.575 ->[0x4A] CH3_CFG4 = 0x00 [0x00]

10:38:19.575 ->[0x4B] CH4_CFG0 =*0x20 [0x00]

10:38:19.575 ->[0x4C] CH4C_CFG1 = 0x00 [0x00]

10:38:19.575 ->[0x4D] CH4_CFG2 = 0xC9 [0xC9]

10:38:19.575 ->[0x4E] CH4_CFG3 = 0x80 [0x80]

10:38:19.575 ->[0x4F] CH4_CFG4 = 0x00 [0x00]

10:38:19.575 ->[0x52] CH5_CFG2 = 0xC9 [0xC9]

10:38:19.575 ->[0x53] CH5_CFG3 = 0x80 [0x80]

10:38:19.575 ->[0x54] CH5_CFG4 = 0x00 [0x00]

10:38:19.575 ->[0x57] CH6_CFG2 = 0xC9 [0xC9]

10:38:19.575 ->[0x58] CH6_CFG3 = 0x80 [0x80]

10:38:19.575 ->[0x59] CH6_CFG4 = 0x00 [0x00]

10:38:19.575 ->[0x5C] CH7_CFG2 = 0xC9 [0xC9]

10:38:19.575 ->[0x5D] CH7_CFG3 = 0x80 [0x80]

10:38:19.575 ->[0x5E] CH7_CFG4 = 0x00 [0x00]

10:38:19.575 ->[0x61] CH8_CFG2 = 0xC9 [0xC9]

10:38:19.575 ->[0x62] CH8_CFG3 = 0x80 [0x80]

10:38:19.575 ->[0x63] CH8_CFG4 = 0x00 [0x00]

10:38:19.575 ->[0x6B] DSP_CFG0 = 0x01 [0x01]

10:38:19.575 ->[0x6C] DSP_CFG1 = 0x40 [0x40]

10:38:19.575 ->[0x6D] DRE_CFG0 = 0x7B [0x7B]

10:38:19.575 ->[0x70] AGC_CFG0 = 0xE7 [0xE7]

10:38:19.575 ->[0x73] IN_CH_EN = 0xF0 [0xF0]

10:38:19.575 ->[0x74] ASI_OUT_CH_EN =*0xF0 [0x00]

10:38:19.575 ->[0x75] PWR_CFG =*0xE0 [0x00]

10:38:19.575 ->[0x76] DEV_STS0 =*0xF0 [0x00]

10:38:19.575 ->[0x77] DEV_STS1 =*0xE0 [0x80]

10:38:19.575 ->[0x7E] I2C_CKSUM =*0x18 [0x00]

DEV_STS 寄存器显示通道已启用且上电。 如您所见、ASI_STS 报告 0xFF、但我不确定其中的原因。

任何指示都将非常感谢。