主题: TLV320AIC3254 中讨论的其他器件

工具/软件:

尊敬的专家:

目前、我们计划使用通过 I2S 上的 PRU 仿真的 I2S 接口。

但是、我们似乎无法为 TAS2781 提供 I2S 信号 Fsync 和 BCLK、

是否有任何音频转换器可以提供这些信号、以便与 AM261 PRU 建立点对点连接、从而使音频放大器直接连接到 AM261x ?

此致、

Alex

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的专家:

目前、我们计划使用通过 I2S 上的 PRU 仿真的 I2S 接口。

但是、我们似乎无法为 TAS2781 提供 I2S 信号 Fsync 和 BCLK、

是否有任何音频转换器可以提供这些信号、以便与 AM261 PRU 建立点对点连接、从而使音频放大器直接连接到 AM261x ?

此致、

Alex

您好 Alex、

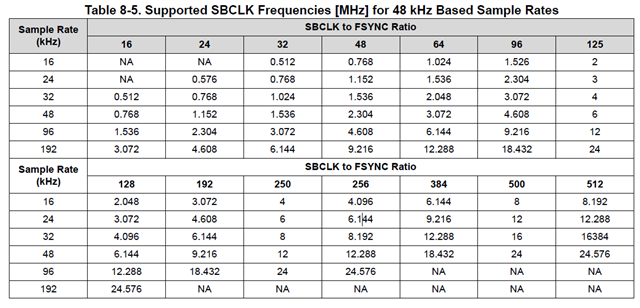

该器件时钟源自 SBCLK 输入时钟。 下表显示了有效的 SBCLK 时钟

每个采样率和 SBCLK 与 FSYNC 之比的频率。

如果通过 SAMP_RATE[2:0]寄存器位正确配置了采样率、则不存在额外的配置

只要 SBCLK 与 FSYNC 之比有效、就需要。 该器件将检测不正确的 SBCLK 频率和

SBCLK 与 FSYNC 之比和音量降低播放路径、以便更大限度地减少可闻失真。 之后钟输出

检测到错误、器件将在 CLK_HALT_TIMER[2:0]寄存器设置的时间后进入低功耗停机模式

DIS_CLK_HALT 位为低电平时的位。 此外、器件可以在有效时钟上自动上电和断电

设置为高电平时发出信号。 在此期间不应更改器件采样率

功能已启用。 在此模式下、DIS_CLK_HALT 位寄存器应设置为低电平、以使此功能正常运行

正常工作。

您好 Alex、

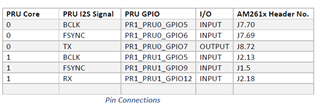

使用连接到 AM261 的 AIC3254 并且它正在工作时。 我假设 AIC3254 处于主模式(意味着 AIC 器件正在生成 BCLK/帧时钟)是否正确? - AM261 PRU 是否无法用作时钟输出?

TAS2781 无法在主模式下工作。 它只能作为 I2S 从器件运行。 这意味着需要应用 BCLK 和 FSYNC。 在您提供的表格中、我看到 BCLK/FSYNC 被标识为输入。 如果这些可以 输出、则它应适用于 TAS2781

此致、

Arthur