Other Parts Discussed in Thread: TAA3040

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1542365/taa3040-channels-not-enabled

器件型号:TAA3040工具/软件:

您好、

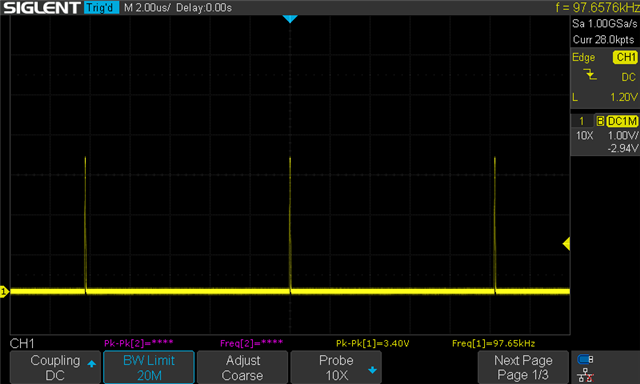

因此、我们正在尝试设置 TAA3040、它具有四个差分输入通道、直流耦合和四个 32 位 TDM 输出时隙。 该芯片通过内部 PLL 从 FS 和 BCLK 进行切换、并且所有时钟设置自动进行。

奇怪的是、即使 我们没有写入 IN_CH_EN 中的使能位(它们复位为启用)、一旦 ADC、MICBIAS 和 PLL 上电、读取 DEV_STS0 寄存器会显示 ADC 断电、DEV_STS1 为 6(器件处于工作模式,所有 ADC 或 PDM 通道都关闭)。

问题:

除了将 SLEEP_CFG 中的器件唤醒为第一个事件并且 PWR_CFG 中的 ADC/MICBIAS/PLL 上电为最终事件之外、是否有特定的顺序来对其他 I2C 寄存器进行编程?

如果在配置芯片之前 FS 和 BCLK 正在运行、则会发生什么情况? 这样会妨碍正确初始化吗?

谢谢

Adam