Other Parts Discussed in Thread: TLV320ADC6140

工具/软件:

您好、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TLV320ADC6140

工具/软件:

您好、

ADC 位于 EVM 板上、因此原理图位于第 21 页: www.ti.com/.../sbau335.pdf

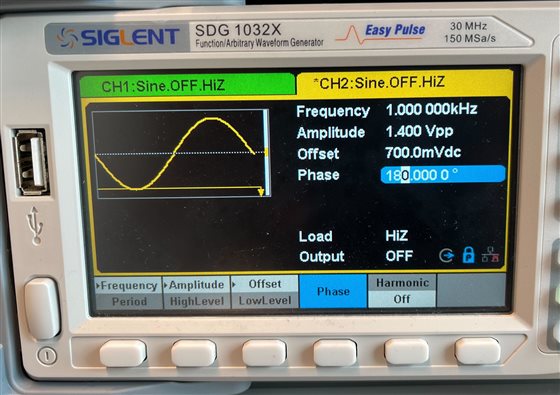

我以差分方式将 AWG 连接到 IN1、并在每个通道上生成 1kHz、1.4Vpp(偏移约为 0.7Vdc,但它是交流耦合)、通道之间偏移 180 度。

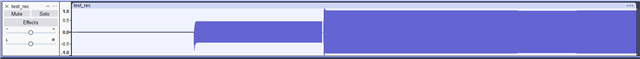

这是我启用 AWG 第一个通道、然后启用另一个通道的记录波形。 (我还验证了原始样本达到接近+- 2^31 值的值)。 在记录的后半部分、我们几乎达到满量程、但每个输入仅接收 1.4Vpp、因此 1Vrms 差分振幅。

这是 init 后的寄存器转储。

I (4728) ADC_ASI_OUT_CH_EN:10000000

I (4768) ADC_ASI_CFG0:00110000

i (4808) ADC_ASI_CFG1:00000000

I (4848) ADC_ASI_CFG2:00000000

i (4888) ADC_DSP_CFG0:00000000

i (4928) ADC_DSP_CFG1:00000000

I (4968) ADC_IN_CH_EN:10000000

I (5008) ADC_ASI_CH1:00000000

I (5048) ADC_ASI_CH2:00000001

I (5088) ADC_CH1_CFG0:00000100

i (5128) ADC_CH2_CFG0:00000000

I (5167) ADC_CH1_CFG1:00000000

I (5207) ADC_CH2_CFG1:00000000

I (5247) ADC_SHDN_CFG:00110101

I (5287) ADC_BIAS_CFG:00000000

I (5327) ADC_PWR_CFG:11100000

谢谢您、

Alan

您好 Alan、

代码绕回 一半额定满量程的一个可能原因可能是 ASI 输出配置不匹配。 我看到您已将 ASI 线路从外部控制器连接到 EVM。 ASI_CFGx 值 表示在 TX_OFFSET = 0 的情况下针对 TDM 协议对器件进行编程。 例如、如果外部控制器正在提供 I2S 信号、或期望 1 个时钟的 TX_OFFSET、这可能会导致位移位、最终导致代码绕回。

如果您使用 EVM、则还需要 ACMB。 考虑到 ACMB 提供 TDM 信号、如果这确实是根本原因、您不应看到代码绕回。 您可以:

1) 使用上述配置使用 ACMB + EVM 验证录制

2) 验证在 ASI_CFG0 (TDM、I2S、LJ) 中编程到器件的协议是否与外部控制器提供给 BCLK/FSYNC 引脚的信号相匹配。

谢谢。此致、

Lakshmi Narasimhan