工具/软件:

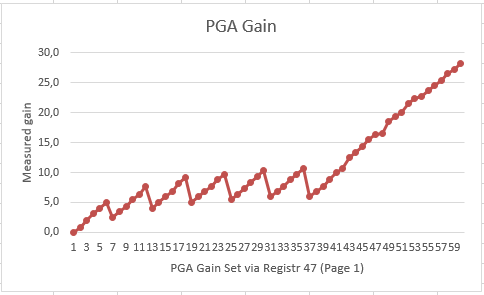

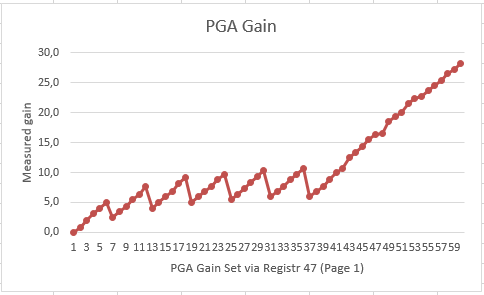

我遇到 PGA 增益设置不一致的问题。 当我逐渐增加页 1 寄存器 47 中的值时、测得的增益不会逐渐增加、但在某些值下增益会下降。 请参阅随附的图表。

增益下降位于以下页 1 寄存器 47 值: 12 (6dB)、24 (12dB)、36 (18dB)、48 (24dB)、60 (30dB)、 72 (36dB)

我应该注意到 AGC 已关闭。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

我遇到 PGA 增益设置不一致的问题。 当我逐渐增加页 1 寄存器 47 中的值时、测得的增益不会逐渐增加、但在某些值下增益会下降。 请参阅随附的图表。

增益下降位于以下页 1 寄存器 47 值: 12 (6dB)、24 (12dB)、36 (18dB)、48 (24dB)、60 (30dB)、 72 (36dB)

我应该注意到 AGC 已关闭。

尊敬的 Jeff:

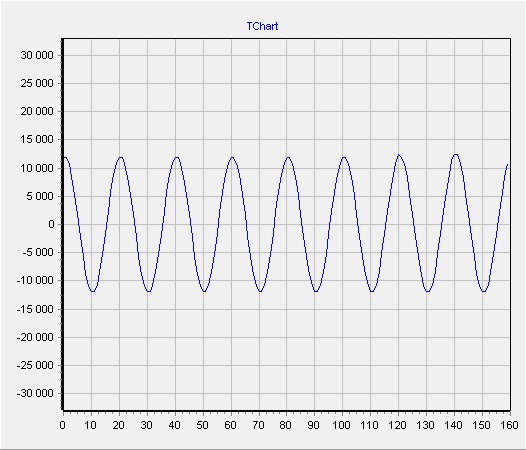

我可以排除削波以及测量工具缩放。 测量布局如下:模拟输入 MIC1LP 由来自信号发生器的正弦波驱动。 音频编解码器的数字输出被传输到数据流。 数据流在 PC 上通过特殊的软件进行分析,该软件可以从接收到的数据中提取信号 — 请参阅随附的文件。 可以看到、输出数字信号没有被削波。 我要指出的是、我们多年来一直使用测量安排、因为我们是 VoIP 通信系统的生产商、并且使用各种音频编解码器(来自 Conexant、Wolfson)。

此致

Stanislav

尊敬的 Jeff:

您是对的、我们会在必要时调整输入信号电平以避免削波。

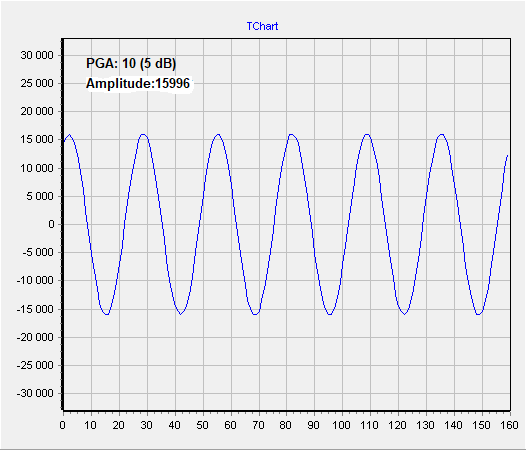

以下是围绕“下降增益点 (6dB)“的测量值:

输入模拟信号振幅:500mV(1V 峰峰值)

ADC 数字增益(页 0 寄存器 83)值:0 (0dB)

PGA 值: 测得的数字振幅:

8 (4dB) 14460

9 (4.5dB) 15484.

10 (5dB) 15996.

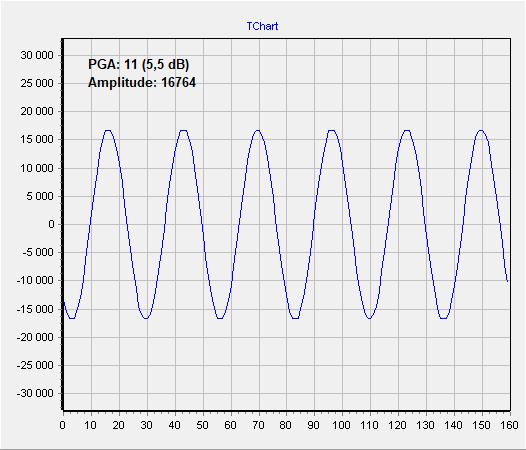

11 (5.5dB) 16764

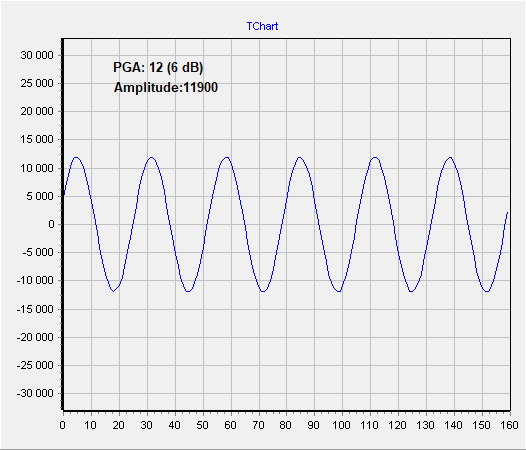

12 (6dB) 11900

13 (6.5dB) 12412

14 (7dB) 13436

注意:

1.我附上几个输出信号图。 我应该注意的是、在数字数据流路径中、G711 mu-law 编解码器会带来量化误差。 无论如何、量化误差很小(约为帐篷 dB)。

2.图形不是 100%完美,因为它们是通过线连接离散测量值绘制的。

此致

Stanislav

尊敬的 Stanislav:

感谢您提供详细信息。 输入电平随着 PGA 增益的增加而降低的确切程度如何? 理论 PGA 增益是 1:1 吗? 即、当 PGA 增益为 4dB 时、输入信号从 1Vpkpk 降低 4dB? 下一个最好的步骤是尝试在我们的最后重新创建这个,因为它不是预期的,从我可以说。

您能否共享起始寄存器配置? 假设测试开始后、PGA 增益是唯一更改的寄存器。

此致、

Jeff McPherson

尊敬的 Jeff:

随着 PGA 增益的增加、我会使输入电平保持恒定、直到输出电平接近最大值为止。 然后、将输入电平降低 6dB。 当然、对于增益计算、我认为降低了 6dB。

以下是寄存器配置(这对寄存器的第一个值是寄存器地址,第二个值是写入值):

// PLL 和时钟设置。 MCLK = 3.072MHz。 CODEC_CLKIN =(PLL_CLKIN*R*J.D)/P =(3.072MHz * 16*2.0)/1 = 98.304MHz。

// DAC_CLK = DAB_PRB = CODEC_CLKIN/NDAC = DAC/8 98.30375MHz = 12.28796875MHz

// DAC_MOD_CLK = DAC_CLK/MDAC = 12.28796875/12 = 1.023997396MHz

// DAC_FS = DAC_MOD_CLK/DOSR = 1.023997396/128 = 7.999979kHz

{0x00,0x00}、 /*--设置第 0 页--*/

{0x33、0x00}、 /* P0/R51 (0x33):GPIO1 禁用(输入和输出缓冲器断电)*/

{0x04、0x03}、 /* P0/R4 (0x04) CODEC_CLKIN = PLL_CLK、PLL_CLKIN = MCLK */

{0x05、0x10}、 /* P0/R5 (0x05) PLL 分频器 P=1、PLL 乘法器 R=16、PLL 断电*/

{0x06、0x02}、 /* P0/R6 (0x06) PLL 乘法器 J=2*/

{0x07、0x00}、 /* P0/R7 (0x07) PLL 分数乘法器 (MSB) D=0 */

{0x08、0x00}、 /* P0/R8 (0x08) PLL 分数乘法器 (LSB)*/

{0x0B、0x08}、 /* P0/R11 (0x0B) DAC NDAC 分频器 N=8。 分频器断电。 */

{0x0C、0x0C}、 /* P0_R12 (0x0C) DAC MDAC 分频器 M=12。 分频器已断电。*/

{0x0D、0x00}、 /* P0/R13 (0x0D) DOSR MSB (DAC OSR) DAC 过采样= 128 */

{0x0E、0x80}、 /* P0/R14 (0x0E)-“"- LSB“ LSB */

{0x12、0x08}、 /* P0_R18 (0x12) ADC NADC 分频器 N = 8。 分频器断电。 */

{0x13、0x0C}、 /* P0/R19 (0x13) ADC mAdc 分频器 M = 12。 分频器断电。 */

{0x14、0x80}、 /* P0/R20 (0x14) AOSR (ADC OSR) ADC 过采样= 128 */

//上电

{0x05、0x90}、 /* P0/R5 (0x05) PLL 分频器 P = 1、倍频器 R = 16、PLL 上电*/

{0x0B、0x88}、 /* P0/R11 (0x0B) DAC NDAC 分频器 N=8。 分频器上电。 */

{0x0C、0x8C}、 /* P0_R12 (0x0C) DAC MDAC 分频器 M=12。 分频器已上电。*/

{0x12、0x88}、 /* P0/R18 (0x12) ADC NADC 分频器 N = 8。 分频器上电。 */

{0x13、0x8C}、 /* P0/R19 (0x13) ADC mAdc 分频器 M = 12。 分频器上电。 */

{0x00,0x03}、 /*--设置第 3 页--*/

{0x10、0x00}、 /* P3/R16 (0x10):内部振荡器用于可编程延迟计时器。 */

//音频接口设置

{0x00,0x00}、 /*--设置第 0 页--*/

{0x1B、0x4C}、 /* P0/R27 (0x1B):编解码器接口控制:DSP 模式、16 位字长、BCLK 是输出、WCLK 是输出 */

{0x1C、0x01}、 /* P0/R28 (0x1C):数据时隙偏移= 1 BCLK */

{0x1D、0x09}、 /* P0/R29 (0x1D):禁用 DIN 至 DOUT 环回、禁用 ADC 至 DAC 环回、BCLK 反转、BDIV_CLKIN = DAC_MOD_CLK */

{0x1E、0x04}、 /* P0/R30 (0x1E):BCLK 分频器 N = 4、BCLK N 分频器未上电。 */

{0x1E、0x84}、 /* P0/R30 (0x1E):BCLK 分频器 N = 4、BCLK N 分频器上电。 */

// DAC 和扬声器设置

{0x3C、0x01}、 /* P0/R60 (0x3C):DAC 信号处理块 PRB_P1。 */

{0x00,0x01}、 /*--设置第 1 页--*/

{0x2C、0x00}、 /* P1/R44 (0x2C):HPL 和 HPR 作为耳机驱动器、默认 DAC 模式*/

// ADC 和麦克风设置

{0x00,0x00}、 /*--设置第 0 页--*/

{0x3D、0x04}、 /* P0/R61 (0x3D):ADC 信号处理块 PRB_P4。 */

{0x00,0x01}、 /*--设置第 1 页--*/

{0x2E、0x00}、 /* P1/R46 (0x2E):MICBIAS 输出断电、器件软件断电未启用。 */

{0x31、0x00}、 /* P1/R49 (0x31):未为 MIC PGA 选择 CM、未为 MIC PGA 选择 MIC1LM。 */

//通话设置

{0x00,0x00}、 /*--设置第 0 页--*/

{0x3F、0x4A}、 /* P0/R63 (0x3F):右通道 DAC 上电、L 通道 DAC 数据路径=关闭、右通道 DAC 数据路径=左数据、DAC 软启动禁用*/

{0x40、0x08}、 /* P0/R64 (0x40):左通道 DAC 静音、右通道 DAC 不静音、左通道和右通道具有独立的音量控制。 */

{0x00,0x01}、 /*--设置第 1 页--*/

{0x23、0x04}、 /* P1/R35 (0x23):DAC_L 不布线到任何位置、DAC_R 路由到右通道混频器放大器、没有其他布线。 */

{0x1F、0x54}、 /* P1/R31 (0x1F):HPL 输出驱动器断电、HPR 输出驱动器上电、输出共模电压= 1.65V */

{0x00,0x00}、 /*--设置第 0 页--*/

{0x51、0x82}、 /* P0/R81 (0x51) ADC 已上电、未启用数字麦克风、禁用 ADC 通道音量控制软步进。 */

{0x00,0x01}、 /*--设置第 1 页--*/

为 MIC PGA 选择了{0x30、0x80}、/* P1/R48 (0x30) MIC1LP、Rin = 20k Ω、 未选择 MICRP、MIT1LM。 */

麦克风音量控制例程设置以下寄存器(在测试期间,我将数字增益设置为 0dB):

{0x00、0x01}、 /*--设置第 1 页--*/

{0x2F、MICPGAGain}、 /* P1/R47 (0x2F):MIC PGA 增益 (0dB ...59.5dB)*/

{0x00、0x00}、 /*--设置第 0 页--*/

{0x53、DigitalGain}; /* P0/R83 (0x53):ADC 数字音量控制粗略调整(–12...20dB)*/

{0x52、0x00}; /* P0/R82 (0x52):ADC 数字音量微调 (0..–0.4dB)。 ADC 静音/取消静音。 */

此致

Stanislav

尊敬的 Stanislav:

我今天能够对此进行测试并验证了您看到的内容 — 输入信号的输出 dBFS 数字“音量“存在跳跃。 我认为我们看到这种行为的原因有几个、还有一些值得探索的有趣途径。

我的第一个建议是在 ADC 的 M 端子上分配某个器件、这是第 1 页寄存器 49 (0x31)。 当设置为共模时、我们会看到输出 dBFS 增加 6dB、并且增益在 6dB 处不再发生跳变。 但是、我们可以更早达到满量程、实际上大约是 5dB 或 6dB 的增益(因为它从那里开始)。 当我们将寄存器 83 更改为 ADC 上最大数字音量减少幅度(–12dB) 时、我们仍然可以在未设置 M 端子时看到增益的跳跃、但在设置 M 端子时、我们会避免增益跳跃、但仍会经历大约 6dB 的失真。 这可能是由于存在这种增益降低情况的阶段所致:PGA 是在输入进入 ADC 之前发生的第一件事、因此如果 ADC 接收到过高的信号、它将无法在保持失真降低的同时以数字方式降低增益。 当信号过大进入 ADC 时、就会发生失真。 我们可以用 THD 测量来测量失真。

我觉得有趣的是、当您没有任何连接到 M 端子的东西时、输出 THD 与 PGA 增益的跳变每 6dB 增益在这几个设置值处发生、然后在~42dB 之后、失真超过增益误差、最终看起来像是削波的、类似于设置 M 端子时我的 6dB 增益在输入信号上的表现。 我测量了许多不同 PGA 增益级别的 THD 与 dBFS 值一起、并发现在增益每次“跳变“后、THD 也变得更糟约 5 至 6dB。 增益突变比这些点的输出预期增加了大约 4dB 至 5dB。 从这些值的相似性可以看出、在内部存在这些 PGA 增益平台、如果正确平衡、信号可能会发生削波、但当 PGA 上没有可“比较“的内容时、ADC 本身可能无法正确识别信号。 只是一个想法。

如果您可以更改该寄存器以将 M 端子设置为共模、然后减少进入器件的模拟信号、我们可以确保 PGA 增益中没有更多奇怪的差异。 但是、我认为这应该能解决您的问题。 很抱歉耽误您的时间。 如果您需要我、我很乐意对此进行更多测试。

此致、

Mir

尊敬的 Stanislav:

是的、之所以发生这 种情况、是因为像您所使用的一样、初始音量为 500mV、约为–5dBFS。 当增益设置为接近此处时、我们会 在 ADC 中看到模拟“削波“、我们可以将其测量为更高的失真、因为它通常包含更多原始正弦波的谐波。 如果输入电平较低、则随着增益值的增加、THD + N 应保持不变。 如果您在此处需要更多帮助、请告诉我

此致、

Mir

尊敬的 Mir:

我明白。

我尝试了将 M 端子设置为共模的配置。 正如您提到的、在这种情况下不会出现“增益跳跃“。 但在此配置中、数字输出信号中存在直流电压偏移(请参阅图像 1)。 直流电压偏移值取决于 PGAGain 和 Digital Gain。 直流电压偏移会减小最大输出信号范围 — 随着输入电压电平的增加,输出信号在正半波中的削波开始比在负半波中早得多(请参阅图像 2;在这种情况下,输入信号有点嘈杂,因此波不理想,但效果明显可见)。 是否有办法可以消除直流失调电压? 至少是一个有关直流电压失调值的可用信息。 我在数据表中未找到任何内容。 我认为该信息非常重要、因为直流电压失调实际上会降低可实现的总体增益。

此致

Stanislav

您好、

您能否提供 寄存器设置? 我们预计信号上会存在一些偏置、由于输入不能低于 0V、因此输入端有交流耦合电容器以允许存在内部偏置。 我认为、使用 VCOM 作为 PGA 的 (-) 侧、我们可以取去耦电容器之后应以 0 为中心的输入与共模之间的差值、以便 ADC 的输出端始终存在共模/偏置。 我认为它与耳机共模相同、使用第 1 页寄存器 31 进行设置。 如果您调整该寄存器、您会看到直 流失调电压变化吗?

-米尔

尊敬的 Mir:

1) 寄存器设置与我 7 月 21 日寄给您的相同,除了:

P1/R49 = 0x80;

P1/R47(MIC PGA 增益)、P0/R38 (ADC 数字音量)-这些寄存器是根据图形上写入的值设置的(请缩放我上次发送给您的图形)。

2) 共模似乎与耳机共模不同。 当我更改耳机共模 (P1/R31) 时、直流失调电压没有变化。

3) 我已经测量了直流电压失调取决于 PGA 增益设置的方式。 结果如下:

PGA 增益: 数字直流电压失调:

0dB 604.

5dB 1052

10dB 1244

15dB 1340

20dB 1308.

25dB 1244

30dB 1148.

35dB 2044

40dB 1836

45dB 3196

50dB 5628

55dB 10108.

59、5dB 16892

有趣的是、在没有任何逻辑的情况下、直流电压失调电压会发生变化。

数字增益设置为 0dB。

此致

Stanislav

尊敬的 Mir:

1)“我们可以保持直流失调电压稳定“是什么意思? 是否有芯片不能超过的任何保证的直流失调电压水平?

2) 我尝试了配置、其中我将输入 MIC1LM 连接到 GND、并将 M 端子设置为 MIC1LM (P1/R49 = 0x20)。 在此配置中,一切正常 — 无直流失调电压。 不幸的是、这种配置并不适合我们、因为我们将 MIT1LM 用于另一个麦克风。

3) 我想再问一个问题。 对于我们而言、未连接 M 端子 (P1/R49 = 0x00) 的配置是可以接受的 — 我们可以执行软件权变措施(在所需增益值与写入 PGA 增益寄存器 P1/R47 的值之间创建一个转换表;当然、PGA 增益的总范围会减小)。 但问题是:

a) 是否连接 M 端子是清洁(正确)的解决方案。 当然、从电路的角度来看、必须连接放大器的反相输入。 但由于数据表只是一个简化的方框图、我不知道这是否真的会成为一个问题。

b) 增益中的跳跃是否可重现 — 是否所有芯片都具有相同的行为。 虽然我们都得出了相同的测量结果、但这并不意味着这是一条一般规则。

此致

Stanislav

尊敬的 Stanislav:

我今天在实验室中连接了器件,我很困惑 — 您看到的是数字信号输出中的直流失调电压? 是否对输入进行交流耦合(包括在输入和输入引脚之间使用交流耦合电容器)? 当我通常向 MIC1LP 施加单端信号进行测量时、我没有看到任何直流失调电压:

但是、当我将示波器探头连接到输入端或交流耦合电容器之后、它会引入一个巨大的 60Hz 尖峰、然后会增加一些直流失调电压:

也许这是您所遇到的情况? 该器件不应处于直流耦合模式、因此请确保您有交流耦合电容器、也许您希望在 I2S 输出上使用 I2S 分析仪、而不是同时探测输入端的任何内容。

请告诉我您的发现。 此外、我将在接下来的几天内离职、因此直到下周中才能够进行实验室测试。

此致、

Mir