Other Parts Discussed in Thread: TAA5242

工具/软件:

您好、

1、在 fs=192kHz 下运行且具有以下设置时、增益为+6dB。 当通过更改 CCLK 在 fs=48kHz 或 96kHz 下运行时、增益也为+6dB。

我在数据表中找不到增益+6dB 的规格、但这种操作是否正确?

2. 如随附的测量结果所示,具有高共模的单端和单端输出电平不同。 无论输入电平如何、输出是否按照该 IC 的规格随引脚设置而变化?

e2e.ti.com/.../TAA5242-MDx-setting-and-Input_5F00_Output-level-_2D00_-_B330D430FC30_.xlsx

<设置>

在 ADC 的控制器模式下进行以下设置。

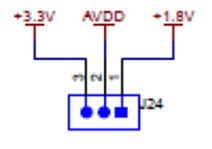

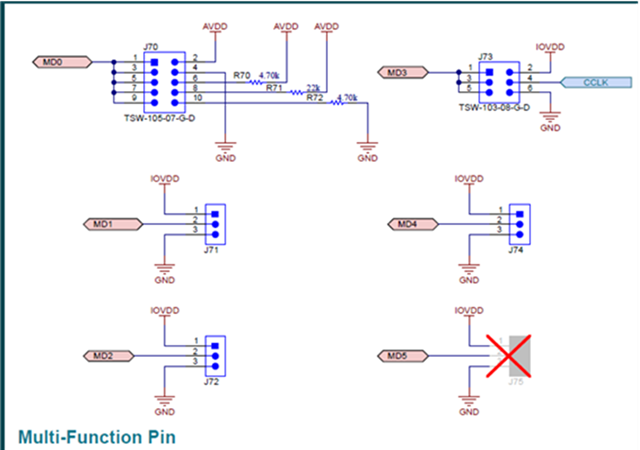

MD0:短接至 AVDD(控制器 I2S 模式)

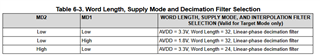

MD2:1:2'b01 (CCLK/128)

MD3:24.576MHz CCLK 输入

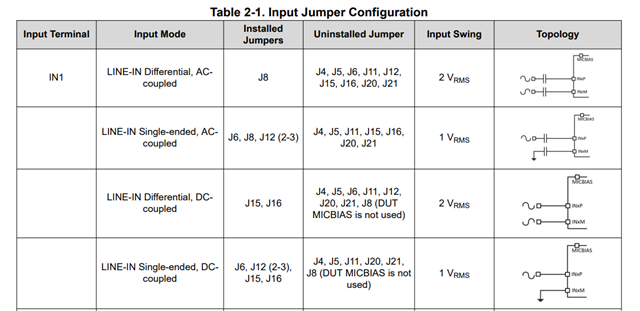

MD5:4:INxP 上的 2'b10 单端输入;仅交流耦合

*为了进行测量,APx555 的数字串行连接至 EVM 外部 ASI 的引脚接头。

此致、

Nishie