Thread 中讨论的其他器件:PUREPATHSTUDIO

工具/软件:

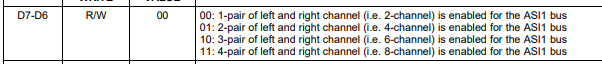

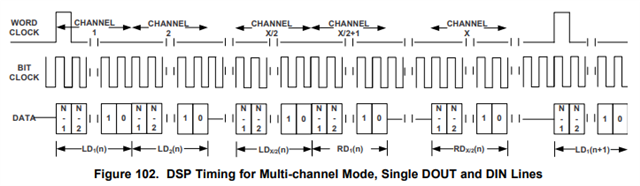

我们仅使用 aic3268 设计了一个系统。 该系统需要将两条 32 位单声道 PCM 总线从 ASI2 和 ASI3 多路复用到 ASI1 上的 8 通道 TDM 总线。 也是在相反的方向上。 因此、两个通道从 ASI1 上 Din 的 TDM 到 ASI2 和 ASI3 的 DOUT。

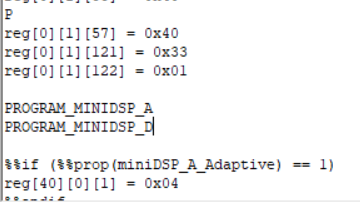

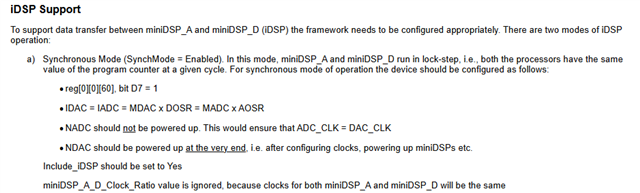

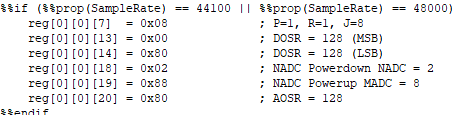

发现对于此配置、我需要对一个或两个 mini-DSP 进行编程。 因此,在此期间,我有 purepathstudio 运行, aic3268 列在框架下。

但是我没有带 TAS1020B 的 USB-i2c 编程器或评估板。 评估板似乎已经停产。

我的问题是:如何在 aic3268 上对 mini-DSP 进行编程?

我确实有一个 EVAL-ADUSB2EBUZ 可用(也有 USB-i2c)。 此外、我还注意到了 https://e2e.ti.com/support/audio-group/audio/f/audio-forum/299026/ttk-reference-designs-for-audio-converters 上的 TK USBtoI2X 软件狗

我可以在任何地方订购这样的加密狗吗? 我可以自己设计吗? 我认为 TAS1020B 需要固件、在哪里可以找到它?

很抱歉有这么多的问题、但我想知道是否可能完成我的工作。