工具/软件:

您好的团队、

来自 ADC 的音频信号输入不是从 DSP 发送到 DAC、而是在输出信号。

尽管 MIC 处于关闭状态(DSP 未发送音频信号)、但 ADC 的信号输入仍为输出信号。

输入格式与图 7-15 中的相同。

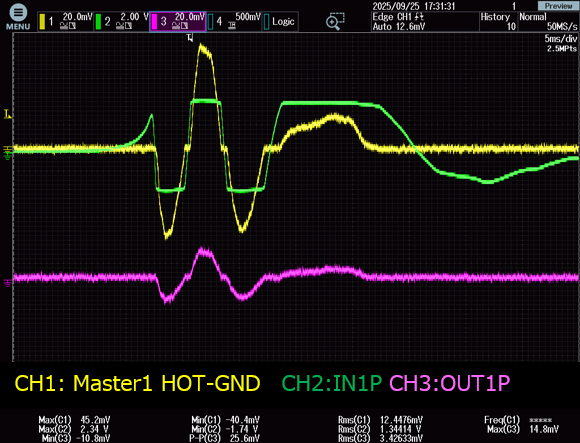

下面附上了波形。

如图所示、当超过 IN1P 和 IN1M 的额定值时、仅在 OUT1P 和 OUT1M 上生成信号。

当施加超过额定值的输入时、什么操作被指定为预期行为?

信号是否可能只从 DAC 侧 CH 泄漏?

寄存器设置如下所示。

w a0 00 00 #设置 PAGE 0

W a0 01 01 #软件复位

W a0 02 09 #使用 AVDD > 2V 且所有 VDDIO 电平唤醒

W a0 0A 00 #GPIO1 被禁用

W a0 0d 02 # GPI1 为 GPI

W a0 0f 60 # CCLK 是 GPI1

W a0 10 50 #将 DOUT 配置为主要 ASI (PASI) DOUT

w a0 1a 60 # PASI I2S、24 位格式

W a0 29 30 # PASI Ch2 位于右侧时隙 0

w a0 32 50 # PASI fs=48kHz、采用自动时钟配置

w a0 34 48 # PLL 始终启用分数并从固定时钟频率启用

w a0 35 02 #MSB=10

W a0 37 f0 #MCLK、48K 的倍数(当 24.576MHz 作为<xmt-block1> 22.5792MHz</xmt-block> 提供时、这会自动移位为输出 44.1k)</s> 22.5792MHz

W a0 38 80 #在控制器模式下使用内部 BCLK 生成 FSYNC

W a0 39 40 #将控制器模式 BCLK/FSYNC 比率设置为 64 = H40

w a0 76 8c 启用输入通道 1;启用输出通道 1、2

W a0 78 c0 #ADC、DAC 上电

此致、

Ryu。