Other Parts Discussed in Thread: PCM5121

工具/软件:

您好、Arash

根据我们在电子邮件中的讨论、我们使用这个 e2e 来跟踪问题调查:

当前进度: 修改 页 0/寄存器 40、然后在 页 0/寄存器 41 中设置所需的移位。

配置方式如下:

除您的建议外、将页 0/寄存器 14 配置如下

您好、王

请在此处更新您的最新 CDST 状态:页 0/寄存器 94 和页 0/寄存器 95

谢谢

Thomas

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好 Thomas、

代码:

uint8_t idx;

uint8_t temp;

sRegWrite (0、0x02、0x00);//“待机 请求“//"Powerdown Request"“ Request" 全部“全部 设为 0、正常模式。

Log_info(“PCM5121: PCM5121 读取 0x02 = %22x… \r\n“、Pcm5121_ReadByte (0x02);

sRegWrite (0、0x04、0x00);

sRegWrite (0、0x0e、0x10);

//sRegWrite (0、0x0d、0x10);

sRegWrite (0、0x0d、0x00);

sRegWrite (0、0x0e、0x30);

对于 (idx = 0; idx < 7;idx++ ){

sRegWrite (0、 pllcfg_96[idx][0]、pllcfg_96[idx][1]);

}

sRegWrite (0、0x25、0x1a);

sRegWrite (0、0x04、0x01);

sRegWrite (0、0x23、0x03);

sRegWrite (0、0x24、0x00);

sRegWrite (0、0x28、0x13);

#if 1 //VCOM 模式

sRegWrite (1、0x08、0x01);

sRegWrite (1、0x09、0x00);//VCOM 上电 。

sRegWrite (1、0x08、0x00);

sRegWrite (1、0x01);//“Output Amplitude Type“ 设置 为 1、 VCOM 模式。

#else //VREF 模式

sRegWrite (1、0x08、0x01);

sRegWrite (1、0x09、0x01);

DELAY_1ms (10);

sRegWrite (1、0x08、0x00);

sRegWrite (1、0x01、0x00);

#endif

sRegWrite (0、0x02、0x00);

LOG_INFO(“PCM5121:PCM5121 读取 0x25 = %22x… \r\n“、Pcm5121_ReadByte (0x25);

sRegWrite (0、61、0x30);

sRegWrite (0、62、0x30);

//sRegWrite (0、0x3D、0x1F); //增益

//sRegWrite (0、0x3E、0x1F);

//Pcm5121_ReadByte (0x28);

//Pcm5121_WriteByte (0x00,0x00);

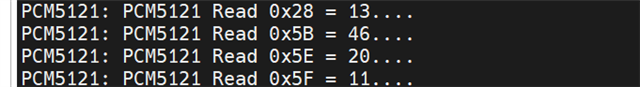

printf(“PCM5121: PCM5121 读取 0x28 = %22x… \r\n“、Pcm5121_ReadByte (0x28);

Pcm5121_WriteByte (0x00,0x00);

printf(“PCM5121: PCM5121 读取 0x5B = %22x… \r\n“、Pcm5121_ReadByte (0x5B);

Pcm5121_WriteByte (0x00,0x00);

printf(“PCM5121:PCM5121 读取 0x5E = %22x… \r\n“、Pcm5121_ReadByte (0x5E);

Pcm5121_WriteByte (0x00,0x00);

printf(“PCM5121: PCM5121 读取 0x5F = %22x… \r\n“、Pcm5121_ReadByte (0x5F);

Log_info(“PCM5121:PCM5121 初始化 成功… \r\n“);

结果:

(__LW_AT__注释:十六进制)

此致

Joseph

尊敬的 Arash:

此 TT 正在跟进我们讨论的电子邮件。 正如我们在电子邮件中讨论的那样、客户希望在 PCM5121 上实现 TDM8 2 插槽工作、尝试过您在电子邮件中分享的建议后、它仍然无法正常工作。

您建议:

1 ) PCM5121 是一个立体声设备( 2 通道) 。 如果要 将 TDM8 的特定 2 个时隙中的数据发送 到器件、 必须转到 页 0/寄存器 41 并对其进行编程、以便它可以利用传入 TDM8 的特定段进行处理

1) 修改 页 0/寄存器 40、然后在 页 0/寄存器 41 中设置所需的移位。

除了你上面的建议,我们还尝试了以下方法,除了你的建议:

1) 分别将采样 FREQ 修改为 48kHz 和 96KHz、并分别修改 FS = 12.88MHz 和 24.576MHz、这两种模式 TDM8 无法工作

2) 配置页 0/寄存器 14 SDAC = 011、选择 SCK 时钟作为 DAC 时钟源、它仍然无法工作。

1) 和 2) 寄存器定义、请参阅此票证的起始帖子图片。

/cfs-file/__key/communityserver-discussions-components-files/6/3730.PCM5xxx_5F00_sample-codes.zip

没有 TDM8 配置、因此客户需要 TDM8 示例代码或帮助他们检查寄存器设置。

上面附加了客户的示例代码。 王先生还更新了那里的最新寄存器设置、如果您需要检查更多寄存器设置、请告诉我们。

-托马斯

大家好、Thomas、我来回顾一下 TDM 操作的一些内容、因为 I2S 和 TDM 几乎相同 、有 2 处不同

假设您有一个使用 I2S(2 个通道)的器件和脚本、现在您要向其发送 TDM8。 您必须注意以下几点:

1-在 TDM 数据序列中、您必须决定要将哪组数据馈送到设备。 要执行此操作、请告知设备(页 0/寄存器 41) 应使用 TDM8 中的哪组数据。 例如、如果我想让 3ed 器件(橙色器件) 使用第二组数据(紫色组)、必须 指示 橙色器件读取 TDM 中的第二组数据(这在寄存器 41 中称为 sift I2S 数据)

2-第二件事你必须注意的是 bck,因为 现在在数据序列中有更多的数据集,它必须工作得更快。 它必须根据以下公式进行设置: BCLK =通道数 *通道 深度 * FS、 (通道深度为 32、24 或 16 等) TDM8 的通道数为 8。

因此、对于 32 位、TDM8 和 48kHz 的 fs、您的 bck 必须是 12.288MHz

通常、如果 CLKS 正常但数据未正确移位、DAC 将处理错误的数据集、但仍然可以工作、并为您提供该数据集的模拟输出、但是、如果 BCK 未正确设置、DAC 将不工作、也不会生成任何输出。

我还检查了以下寄存器的读取操作、寄存器 95 似乎表明存在错误。

寄存器 0x28 (40)= 0x13 ==> 00001 0011 TDM 、32 位 (正常)

寄存器 0x5B (91)= 0x46 => 0100 0110 FS 检测到:88.2-96KHz 、SCK = 256 XFS (正常)

寄存器 0x5E (94)= 0x20 ==>0010 0000 PLL 已锁定、所有 CLKS 均存在且有效 (正常)

寄存器 0x5F (95)= 0x11 => 0001 0001 LTSh(1:自上次读取后发生了 SCK 停止)CERF (1:时钟无效(错误))

因此、只有寄存器 95 (0x5F) 指示 CLKS 存在一些问题。 寄存器 14 似乎可以将 SCK 用作 DAC 的源。 我可能想阅读 reg 28, 29 30 和 34 稍后 (页 45 的数据表 , 时钟分布),但暂时我想先回顾以下内容:

您能否向我发送 以下信息:

您能否确认是否能够使用简单的 I2S 格式? 我强烈建议您首先使用 I2S 格式运行、一旦一切正常、我们可以向芯片引入新格式 (TDM8)。

此致、

Arash

您好、Arash、

1.读取 0x1C 0x0B

读取 0x1D 0x03

读取 0x1E 0x03

读取 0x22 0x00

2.bck 24.576M

SCK 24.576M

LRCLK 96K

VNEG - 3.3V

LDOO 1.8V

4.修改了下面的原理图。 SCK 接受来自 DSP 的 MCLK 24.576M 输出。

如上面的原理图所示、当 SCK 接地时、I2S 输出是正常的。 更改 SCK 后、I2S 输出异常。

此致、

Joseph

您好、Joseph:

感谢您提供更多信息。 我仔细研究了原理图、登记册上的内容告诉了我、下面是我的观察结果和问题:

请提供我在上一帖子中要求的 I2S 图(请参阅上面帖子中的图)

读取 DAC 时钟的 0x1C (28) 0x0B===>11 源时钟分频器值。 在时钟自动设置模式下会忽略这些位。

读取 0x1D 0x03 =====> CP 时钟的 3 个源时钟分频器值

读取 0x1E 0x03 ====>3 OSR 时钟的源时钟分频器值

读取 0x22 (34) 0x00 ===> 00:单速 (FS≤48kHz)

不过、昨天您发帖时、我正在读取 寄存器 0x5B (91)= 0x46 => 0100 0110 检测到的 FS:88.2-96KHz 、SCK = 256 XFS

您还提到了 FS=96K, 那么请检查这种差异 吗?

TDM8 和 32 位的 CLKS 速率为 96K、BCK 为 24.576M 看起来可以。 此外、根据数据表的表 32、可以使用 24.576M 的 SCK。

您已将 ADR1 和 ADR2 连接到 GND 、因此地址为 X98、示意图上的注释显示地址 0x99 。 我相信 这是一个简单的拼写错误,你有. 您能否仔细检查一下以确定是否属实。 地址只能是 0x98、0x9A、0x9C 和 0x9E。

我不清楚项目 5 在你上面的帖子.

因此是否连接了 SCK? 我们的调试必须保持一致。

如果 SCK 接地,则不能在任何 多路复用器中选择 SCK 作为 clk 的来源。 但是、从您之前的帖子中、至少 寄存器 14 具有 SCK 作为 DAC 的源。

从原理图中、SCK 和 I2S 是从 DSP 向 DAC 提供的外部信号、那么 SCK 如何使 I2S 异常? “你说什么? 器件是否处于主模式并从主时钟生成 I2S 、以及与 DSP 发送的内容发生冲突?

此外、根据表 33、对于 PLL 操作、fs 的最大 BCK 为 96K 6.144MHz; 这意味着 PLL 不接受 TDM8 所需的 BCK (24.576M)。 因此、您需要提供 一个有效的 SCK 并使用 SCK 作为时钟源 、而不是 PLL。

请注意、寄存器 0x5F 也表示时钟错误。

寄存器 0x5F (95)= 0x11 => 0001 0001 LTSH(1:自上次读取后发生了 SCK 停止)CERF (1:时钟无效(错误)) 。

请读取寄存器 37 (0x25) 以查看是否启用了自动时钟设置。

请仔细阅读我的帖子、仔细检查设置并进行更正、让我知道它是如何进行的。

此致、

Arash