Other Parts Discussed in Thread: TLV320AIC3104

器件型号: TLV320AIC3104

这是我以前提出的错误标记为“已解决“的问题的延续

我有 TLV320AIC3104 开发套件。 它连接到 ESP32 S3。 我将 I2S 设置为“INTFACE"</s>“

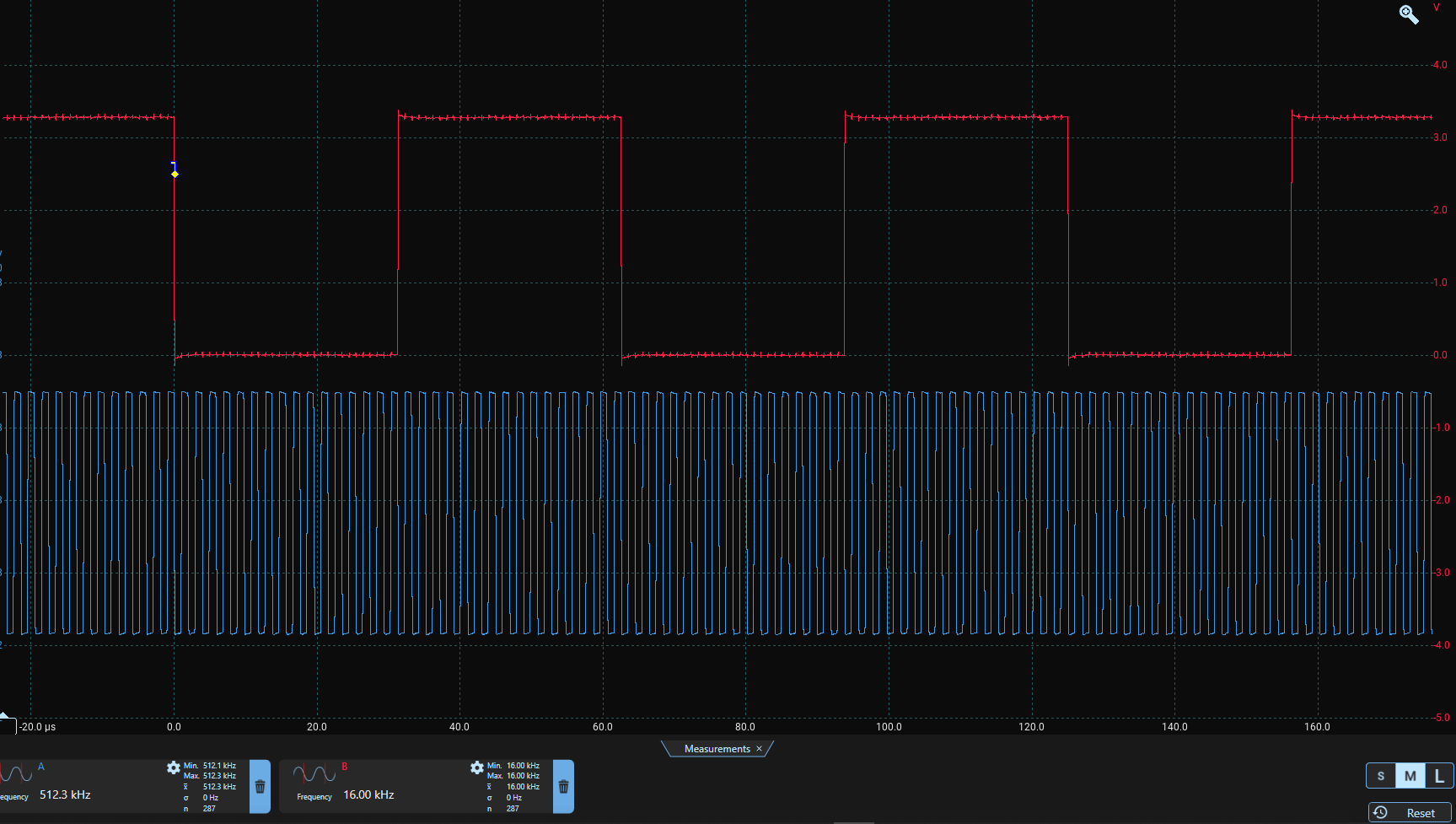

Wclk = 16KHz、BCLK=512KHz、

下面的示波器图显示了波形。

我正在使用 AIC310x EVM GUI。 如果我使用预设配置“静置回放交流耦合耳机输出“并写入低频 (100Hz-300Hz) 正弦波形、则结果是干净的。 但在 fs=16KHz 时有一个通知的背景嘶嘶声。 随着我增加 FS、嘶嘶声开始消失。 在 32KHz 以上、则无法检测到。 它与采样率有关。 在 11.025kHz 时、嘶嘶声非常普遍。

即使 I OUTPUT 是直流值、也存在嘶嘶声。

所以、我尝试使用下面列出的脚本使用 PLL 来使我进入 48kHz 模式。 我尝试了设置寄存器 4 以将 PLL 设置为 16KHz 和 48kHz 在任一情况下、都没有生成音频。 我已经确认将正确的实例写入寄存器。 将 R07 设置为 0x8A 或 0x0A 不会有任何区别。

我已经为这个问题努力了大约一个月。 我在做什么? 我是否需要提供 MCLK 信号? 我不应该听到任何嘶嘶声。 唯一没有嘶嘶声的情况是我复位器件时。 所以我认为这不是模拟问题。 我对其他供应商的其他编解码器没有这个问题。

--布拉德·斯图尔特

48kHz 模式下的#、wclk=16kHz、BCLK=512khz(16 位 2 通道)

#对于 16KHz 模式、设置 J=8?

W 30 01 80 #软件复位

W 30 02 66 #ADC 且 DAC FS = FS (ref)/4

w 30 03 92 #PLL 已启用、Q=2、P=2

W 30 04 60 #J=24

#w 30 04 10 #J=8

W 30 05 00 #D=0

W 30 06 00 #D=0

W 30 07 0A #FS (ref)= 48K、LDAC 和 RDAC 路径开启

W 30 0b 00 #R=16

w 30 65 00 #CODEC_CLKIN 使用 plldiv_OUT

w 30 66 a0 #clkdiv_IN 使用 BCLK、pllclk_IN 使用 BCLK

w 30 29 02 #DAC_L1 和 DAC_R1 路径

w 30 2b 00 #LDAC 未静音、增益= 0dB

w 30 25 d0 #l+r DAC 上电、hplcom 是恒定的 Vcm 输出

W 30 26 20 #hprcom 是外部反馈、hplcom 作为恒定 VCM

W 30 40 80 #DAC_R1 路由到 Hprout

W 30 2f 80 #DAC_L1 路由到扩展输出

W 30 33 0d #hplout = 0dB、无静音、完全上电

W 30 41 0d #对于 hprout 相同