请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:PCM4201 PM4201

- PCM4201的主模式和从模式有何不同;在我的情况下,他们使用了哪些应用程序来实现通过麦克风阵列的音频源本地化,我将使用 FPGA 作为控制器。(顺便说一下,是否可以将此 ADC 与 FPGA 连接?)

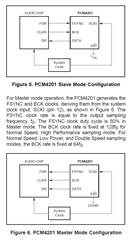

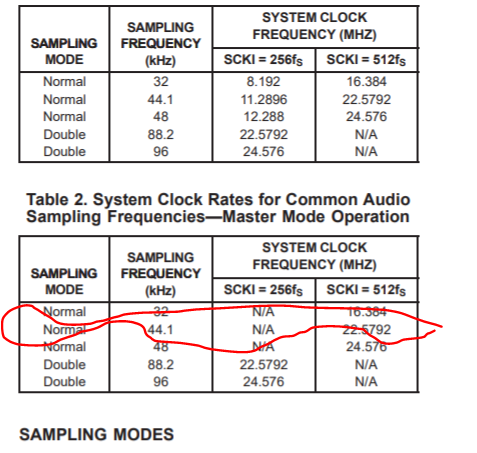

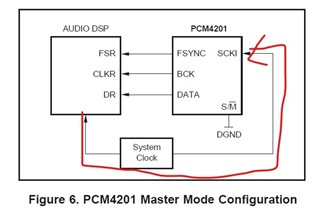

- 系统时钟用于提供采样频率参考,它用于音频 DSP 和 ADC。 但在主模式下 ,PCM4201会生成用于通信的 FSYNC 和 bck 时钟,然后我会询问此系统时钟对音频 DSP 的用途是什么?