Other Parts Discussed in Thread: TAS2563, TAS2X63EVM

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1079848/faq-tas2563-pdm-interface

部件号:TAS2563“线程: TAS2X63EVM”中讨论的其它部件

如何在 TAS2563中配置 PDM 接口?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TAS2563, TAS2X63EVM

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1079848/faq-tas2563-pdm-interface

部件号:TAS2563如何在 TAS2563中配置 PDM 接口?

TAS2563支持 PDM 麦克风输入。 两路 PDM 麦克风输入简化了双向音频系统的音频信号链,将数字麦克风与主机处理器连接起来。

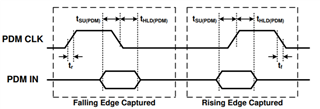

除了电源外,PDM MIC 通常需要两个信号才能工作。 它是 PDM CLK 和 PDM 数据。 PDM 数据可以在 PDM CLK 的上升边缘或下降边缘获得。

设置后,其中一个 PDM MICS 在 CLK 提升边缘工作,另一个 PDM Mic 在 CLK 下降边缘工作,两个 PDM MICS 可以连接在一起。 芯片组将在上升边缘和故障边缘读取数据,然后将它们分成两组数据。

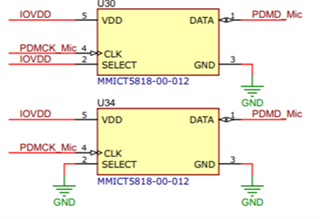

例如,PDM 麦克风有5个针脚,如下表所示。 “‘s针脚”可以设置为高或低,以确定哪个信号级别可用于麦克风数据。

| 引脚编号 | PIN 名称 | 类型 | 描述 |

|---|---|---|---|

| 1. | 数据 | 数字 O | PDM 输出 |

| 2. | 选择 | 数字 I |

低/高(L/R)选择 连接至 VDD 或 GND |

| 3. | 接地 | 电源 | 接地 |

| 4. | 时钟 | 数字 I | 时钟输入 |

| 5. | VDD | 电源 | 电源 |

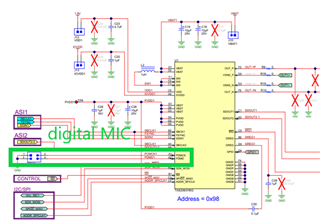

在 TAS2x63EVM 上,两个多指标类集调查连接在一起,但所选引脚在不同级别设置为低或高。 这两个多指标类集调查在系统中独立工作。

PDM 输入由 PDMCLK 引脚采样,PDMCLK 引脚可配置为 PDM 时钟从输入或 PDM 时钟主输出。 PDM_MIC_EDGE 和 PDM_MIC_SLV 寄存器位选择采样时钟边缘和主/从模式 PDM 输入。 在主模式下,PDMCLK 引脚可以通过将 PDM_Gate_PAD0寄存器位设置为低来禁用时钟(和驱动逻辑0)。 当配置为时钟从属设备时,PDM 时钟输入不需要与系统时钟的特定相位关系(在 TDM/I2S 模式下为 SBCLK),但必须与音频采样率来自相同的源。 这相当于单速/双速/四速采样率的16年64月32日 (~3 MHz)或1 32年28月64日 (~6 MHz)倍。 PDM 速率由 PDM_RATE_PAD0设置。 当 PDMCLK 引脚配置为时钟主控时,TAS2563将输出由 PDM_RAM_PAD0和寄存器位(16年64月32日 或1 32年28月64日 是单速/双速/四速采样率的倍)设置的50%占空比时钟。

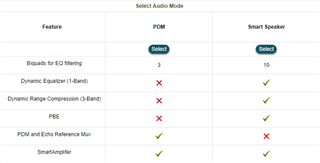

内部 DSP 处理功能被重新利用以启用 PDM 界面,请注意 PPC3软件列出的每种情况的不同之处。

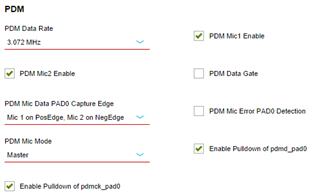

PDM 硬件接口配置可在设备控制面板中配置,如下图所示。

每个通道的数字增益控件可通过“调谐和音频处理”面板访问。

用于反馈 PDM Mic 数据的 ASI 配置可在 End System Integration (终端系统集成)面板的快照选择步骤中使用,如以下捕获中所突出显示。