您好,

在我们的项目中,我们连接了2个 TLV320adc6140 (TDM,菊花链),以获得8个输入通道(模拟)。

CPU 是主 CPU (提供 FSYNC/BCLK 并在同一 RX 系列中获取所有样本)

——我在数据表中找不到每个 ADC 输入样本之间的关联时间是多少?

所有通道都是同时采样 的??? 两者之间的差距是多少? picoSEC / nanoSEC???

——是否涉及任何软件注册并可以批准? 或者这是纯粹的硬件。

此致,

莫兰。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

在我们的项目中,我们连接了2个 TLV320adc6140 (TDM,菊花链),以获得8个输入通道(模拟)。

CPU 是主 CPU (提供 FSYNC/BCLK 并在同一 RX 系列中获取所有样本)

——我在数据表中找不到每个 ADC 输入样本之间的关联时间是多少?

所有通道都是同时采样 的??? 两者之间的差距是多少? picoSEC / nanoSEC???

——是否涉及任何软件注册并可以批准? 或者这是纯粹的硬件。

此致,

莫兰。

你好,Sanjay,

硬件:

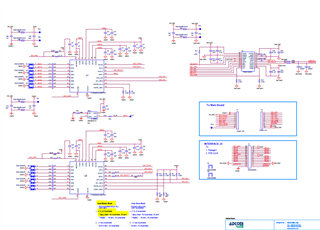

您可以从下面的设计原理图中找到相关的捕获。

请忽略所有选项和 DAC,将其视为以黄色标记-->路由

NXP CPU 是 以菊花链方式连接的两个 tlv320adc6140的主 CPU。

目前我正在处理2个提供相同配置的 EVB。

软件:

在使用 pyAudio 的 Linux (ALSA 库)下,我们将并行捕获所有8个通道(24位/48K)

——请告诉我是否需要注册地图,或其他信息。

巴西,

莫兰。

我注意到 U2上的 MIC5至 Mic 8输入未命名为 net。因此它们未连接到 J3。

将 MCLK 输入到 UI 的目的是什么?您可以将 ADC 设置为从属设备,并将 BCLK 和 FSYNC 设置为输入。

1)我错误地上传了一个不带 net 名称的旧版本。 感谢您的注意。

2)据我了解,有多个连接多个 TLV320ADC6140的选项,因此我们在音频卡上实施了所有选项。

我们的默认配置:两个 ADC 都是从节点,BCLK 和 FSYNC 作为输入(来自 IMX8M CPU)。 Daisy 链是输出插槽的选择。

关于 MCLK:如果我们希望 ADC 成为主控制器,“GPIO1配置为主时钟输入(MCLK)”。

请告知 是否所有8个通道的同时采样会受到设置(主/从/菊花链/MCLK)的影响。