尊敬的专家:

我们要将 WCLK设置 为44.1kHz,MCLK=24MHz。

但是 ,设置参数后,WCLK输出不正确(以38kHz显示)。

参数设置如下:NDAC=8, MDAC=1, DOSR=128, J=4, R=4, P=5, D=704, PLL_CLKIN_DIV=2 (PLL CLK选择 MCLK)

基于公式DAC_FS=DAC_CLKIN/(NDAC*MDAC*DOSR)

DAC_CLKIN=PLL_CLK_OUT =(PL_CLKIN*R*J.R)/(P*PLL_CLK_IN_DIV)=(2400万*4*DV)/(5*2)=45158400<xmt-block0>4515.84万 4.704

DAC_FS=4515.84万/(8*1*128)=4.41万

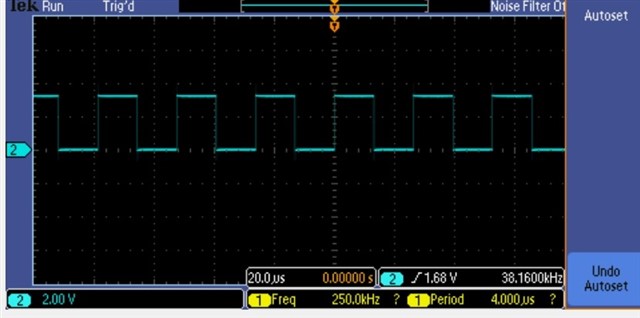

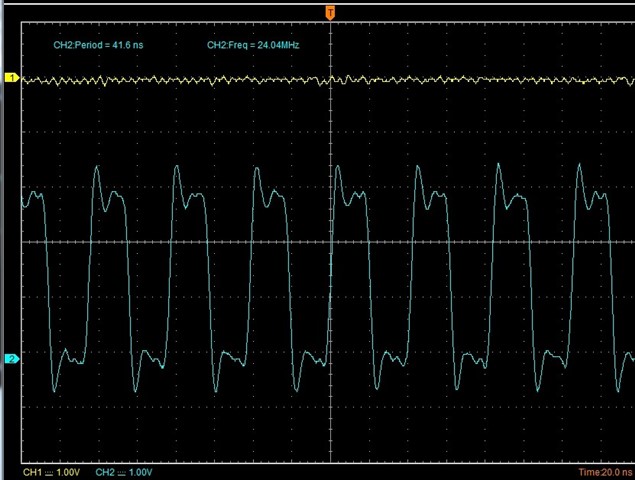

波形如下所示:

WCLK:(38KHz)

MCLK:(24MHz)

我们在计算中是否有任何遗漏或错误,从而无法获得44.1kHz WCLK输出?

谢谢你。

此致,

辛迪