对谁来说,

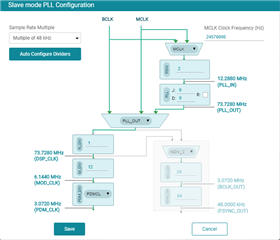

我想对该部件进行编程,以便从PurePath控制台使用下面显示的PLL配置。 我没有在数据表或PurePath控制台寄存器映射中看到分隔器寄存器设置。 要实现该图,需要哪些寄存器,寄存器地址和寄存器设置? 这些寄存器看起来是PLL输入选择(MCLK或BCLK),PDIV,J,D,N_DIV,M_DIV, 和3输入时钟MUX选择馈入N_DIV。 在系统中,我将提供3.0720MHz的BCLK和48kHz的FSYNC。

谢谢!

肖恩

附注 :数据表中似乎相关的寄存器为MST_CFG0,MST_CFG1,CLK_SRC和PDMCLK_CFG。 根据数据表说明,大多数设置不在从属模式下使用,自动时钟配置已禁用,自动时钟配置中已启用PLL。