https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1086406/pcm4104-no-output

部件号:PCM4104我正在使用定制板上的PCM4104进行开发,但没有任何输出。 我期待1 kHz正弦波。

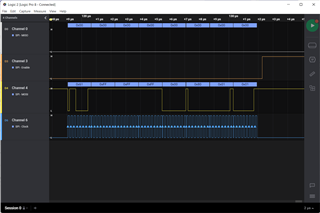

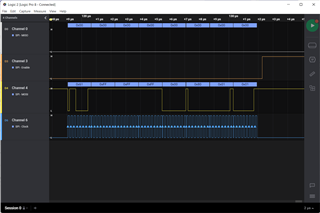

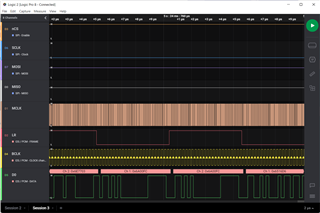

以下是我的SPI配置(软件重置后):

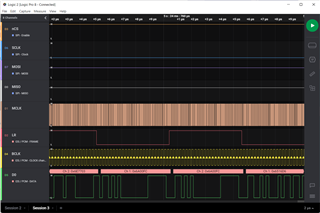

我正在发送24位I2S音频数据(满刻度24位正弦曲线):

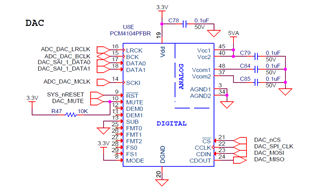

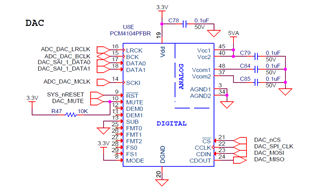

这是零件的示意图:

参考电压为+5 / GND。

我们非常感谢任何帮助。

账单

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

https://e2e.ti.com/support/audio-group/audio/f/audio-forum/1086406/pcm4104-no-output

部件号:PCM4104我正在使用定制板上的PCM4104进行开发,但没有任何输出。 我期待1 kHz正弦波。

以下是我的SPI配置(软件重置后):

我正在发送24位I2S音频数据(满刻度24位正弦曲线):

这是零件的示意图:

参考电压为+5 / GND。

我们非常感谢任何帮助。

账单

Bill,某种情况不正确,因为原理图显示静音被拉高,您确认它被拉低,我认为您的原理图和实际连接存在许多其他差异,或者这不是正确的原理图。

未提及电源定序b/w数字和模拟,但以下是开机时发生的顺序:

开机时,内部重置信号被强制为低电平,强制PCM4104进入重置状态。 通电复位电路监控VDD,VCC1和VCC2电源。 当VDD超过+2.0V (误差幅度为±400mV)且VCC1和VCC2超过+4.0V (误差幅度为±400mV)时,内部复位信号会强制为高电压。 然后,PCM4104等待系统时钟输入(SCKI)变为活动状态。 检测到系统时钟后,初始化序列开始。 初始化序列需要1024个系统时钟周期才能完成。 初始化序列完成后,PCM4104将准备好在音频串行端口接受音频数据。 图5显示了开机重置顺序计时。 如果通过SPI端口将PCM4104配置为软件模式控制,则所有控制寄存器将在初始化序列期间重置为其默认状态。 在独立模式和软件模式下,所有四个通道的模拟输出在重置和初始化序列期间均被静音。 在静音状态下,模拟输出引脚被驱动至双极零电压或VCC/2。 .

某些寄存器(如Register 6: System Control Register)可以禁用信道,使用相同的令牌,您的clk设置,R/LJ和...可能不正确。

此外,停止DAC输出所需的一切 都是一个连接 不正确的引脚。 请将完整的示意图与所有连接一起发送,以便我查看。

另外,请 捕获 并发送关键波形,如所有CLK,RESET,....

谢谢!

Arash

Bill,为了调试问题,我们通常需要完整的原理图 来查看 每个引脚(如PU和PD电阻器)与引脚(如FMT,FS和...)的连接情况。 如果您认为原理图是正确的,我们就会这样做。

我不知道您正在使用 VREF+或VREF-执行什么操作,它是否连接到正确的电压? 您是否读取VCOM上的任何电压?

下一步是确保正确写入 寄存器,很少回读会有助于验证此情况, 特别是寄存器(如reg 5,6和7)。

您可以探测几个关键信号并查看部件是否从复位中退出:从耗材开始 ,芯片选择, 复位以及所有CLKS。 您要确保CLKS (1)有效且在规格范围内,并且(2)是 通过 探测它们按预期生成的(例如 ,我无法从您的图解中读取MCLK的频率)

此致,

Arash

Arash,

再次感谢您的帮助。 我和同事在发布前处理了这个问题一个星期;这不太可能是明显的。

FS和FMT引脚是浮动的。 MCLK频率是36.864 MHz,我已经验证过。 VCOM为2.5 伏特。

十六进制寄存器为:

1 FF

2 FF

3 FF

4 00

5 80

6 01.

7 01.

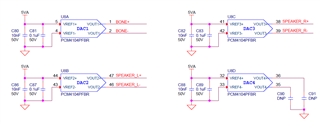

我没有列出输出部分,因为它们相当无聊:

然后,输出直接馈入重建滤波器,如数据表中所示。

此致,

账单

1 FF 1111 无衰减0.5x (255-255)= 0dB

2 FF 1111 1111

3 FF 1111 1111

4 000000 静音

5 801000 0000 MUT4=静音,MUT(3:1)=开 , 零日期静音:禁用,相位:非inv, DEM:默认

6 010001 0000 无复位,所有4通道断电均已禁用,单速率

7 010001 0000 24位左对齐,LRCKP: LRCK极性反相,BCKE Bck采样边:上升边

我检查了所有的寄存器,看起来一切都很好,我没有看到任何异常的东西,我可以建议的唯一变化是尝试I2S数据,并使用极性 和边缘选项,基本上 寄存器7值,以确保它们与您的来源匹配 (如AP)设置。

此致,

Arash

Bill,现在您已经验证了主板在LEFT REGISD和96KHz的情况下工作,问题似乎出在 源与IC (根据寄存器值)之间的握手。

您需要 确保 在 源位置选择I2S格式时,寄存器也在脚本中被编程为I2S 。 AP是我们用于测试的主要用途,假设您也在使用AP,您必须谨慎选择 所选的选项。 例如,如果我反转WfM,我的芯片将停止工作,但当我反转并使用位宽脉冲时,它仍然工作。 我之前提到的其他事情是数据层的下降/上升边缘 以及下降/上升边缘同步。

此致,

Arash