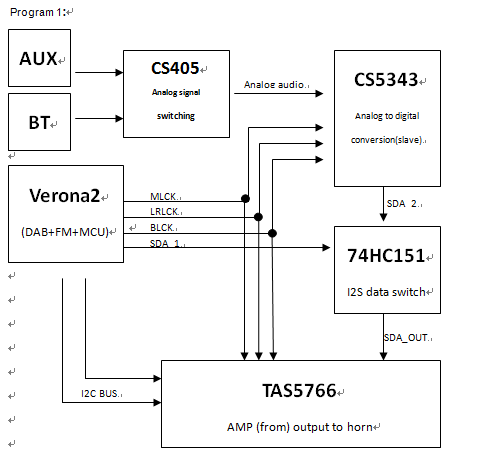

对于TAS5766的设计,请根据客户要求(例如描述两组程序的附件)帮助确认两个程序的可行性

1 TAS5766的程序1/2在很大程度上被I2S MCLK主时钟线路省略,是否可行? 它对TAS5766有何影响?

2在第一个方案中,即数据线路中的I2S总线开关,它是否会影响I2S的定时? TAS5766?

3在第一种方案中,数据线路中的I2S总线在交换机(如74HC151)之后,另一条线路不通过,将影响I2S的定时?

4在第二个方案中,整体开关I2S总线,如果我的I2S采样频率不同,TAS5766 CAN制动器识别?

5在第二个方案中,整个交换机I2S总线,如果我的I2S采样频率相同,对TAS5766的影响是什么?

6.如何在播放时更新I-RAM Block,C-RAM Buffer A/B数据? 您能否提供一个示例?