请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

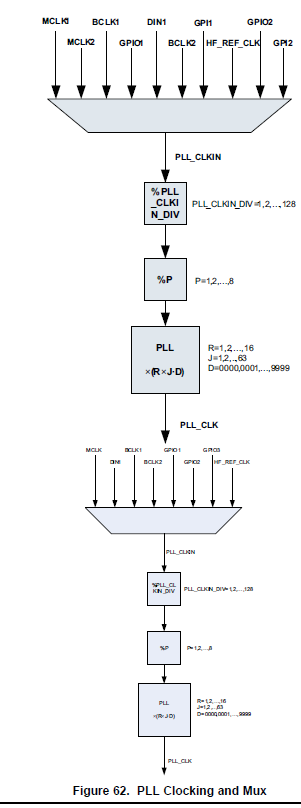

部件号:TLV320AIC3268 我正在计划使用上的,将TLV320AIC3268用作I2S主控,并将PLL用作时钟源。 从 HF_REF_CLK获取PLL_CLKIN。

- 开机时,您必须提供时钟信号(从图63中选择)以校准HF_OSC _CLK。 LFR_CLKIN的推荐频率范围是多少?

- 我看到一条注释,指出频率可能会关闭约±7MHz。 这对性能有很大影响吗? 不确定这是否是一个大问题。 如果能够提供更好的性能,我可以让另一个设备提供时钟信号。 然后,我会使用另一个输入(图62)来输入PLL_CLKIN,而不是HF_REF_CLK。