尊敬的各位先生:

我的客户向我们询问了TAS5760M用于硬件控制的电源开/关顺序。

有一种现象是在主板上通电时不输出。

此时,ANA REG电压为10 V,电压异常。 (正常为3.3V)

因此,我认为在开/关顺序上有一个因素。

在这种情况下,你是否有什么可以被认为是一个原因?

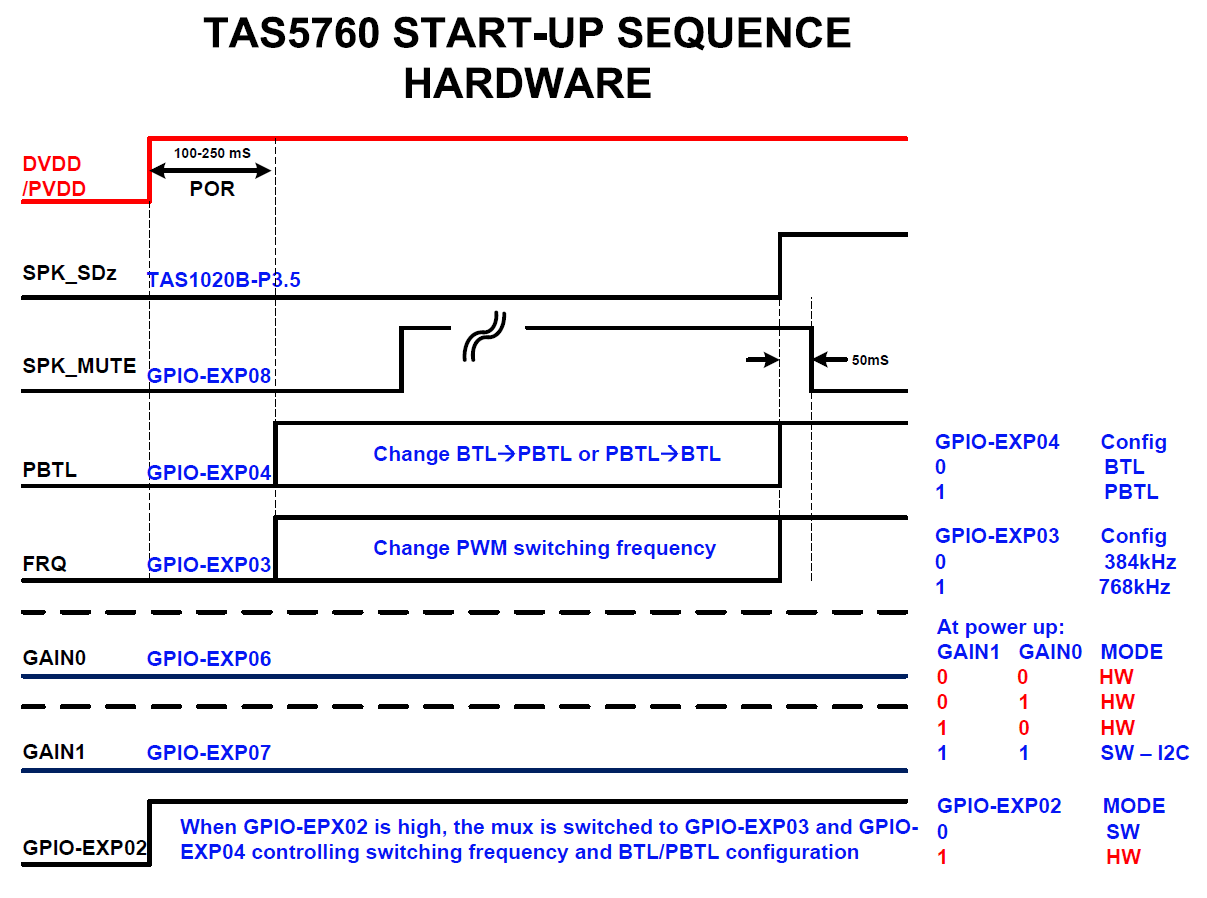

他的开机顺序如下。

1.打开电源后,将SPK_SD设置为“低”,将SPK_SLEEP / ADR设置为“高”。

稳定电源并设置硬控制针脚后,将SPK_SD设置为"高"。

3.释放关机后,将SPK_SLEEP / ADR设置为"低",并在SPK_SD变为高SPK_SLEEP / ADR被释放后约3秒钟。

这是否正确?

关机顺序为

SPK_SLEEP /ADR为HIGH后SPK_SD为LOW,电源关闭后输出关闭。

这是否正确?

此致,

是。哈塞伯