https://e2e.ti.com/support/audio-group/audio/f/audio-forum/640766/tlv320aic3106-white-noise

部件号:TLV320AIC3106主题中讨论的其他部件:AM3352

我们正在通过AM3352上的McASP驱动编解码器。我们似乎通过I2C或数据线与编解码器通信没有问题

我们处于DSP模式,16位,8kHz FS。编解码器是FS和WCLK的主编解码器。 输入是24.576MHz振荡器。我们是在定制板上,而不是EVM上

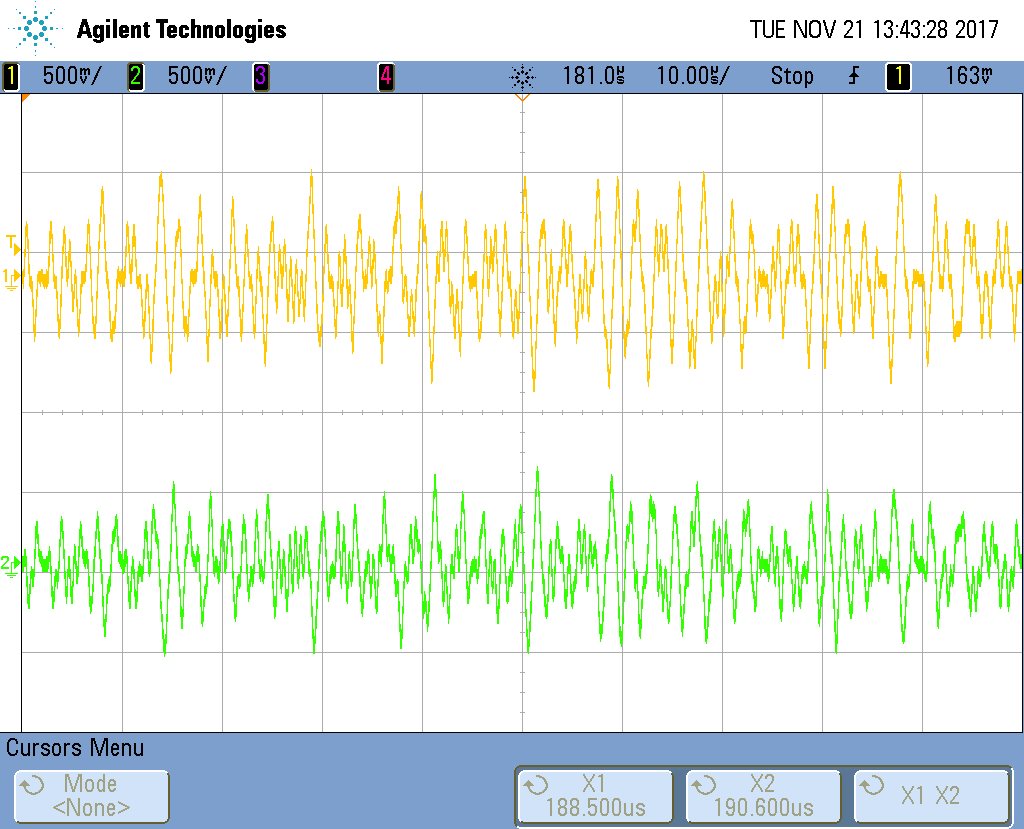

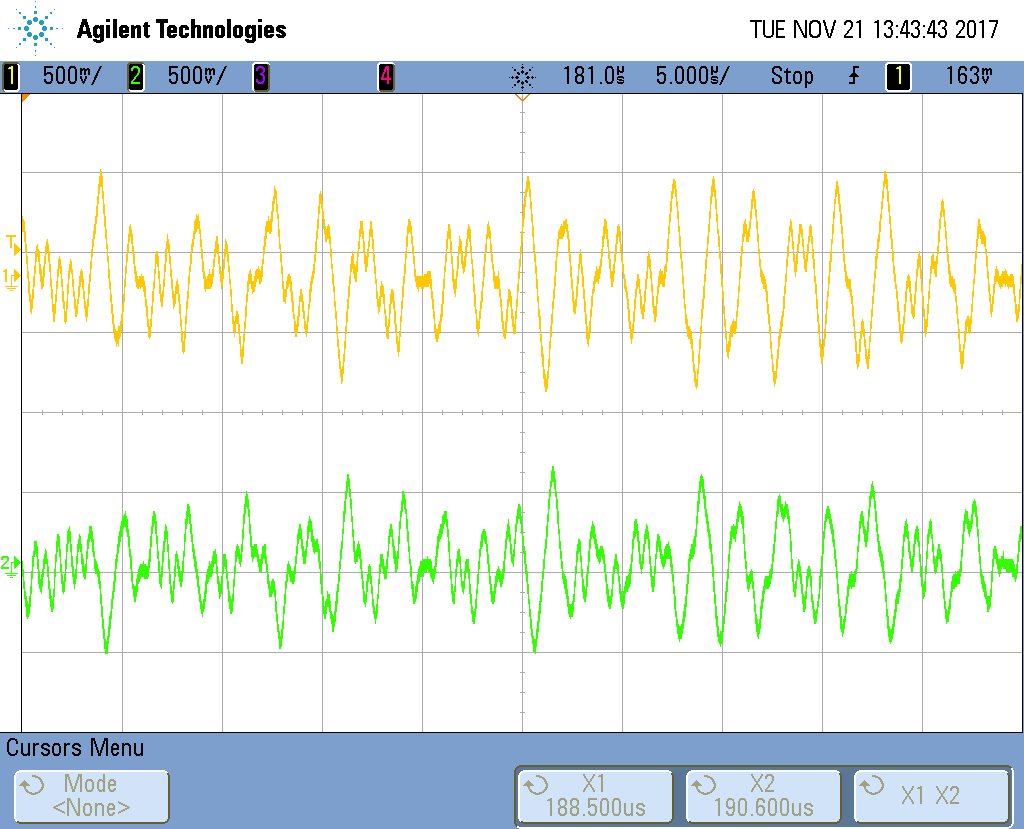

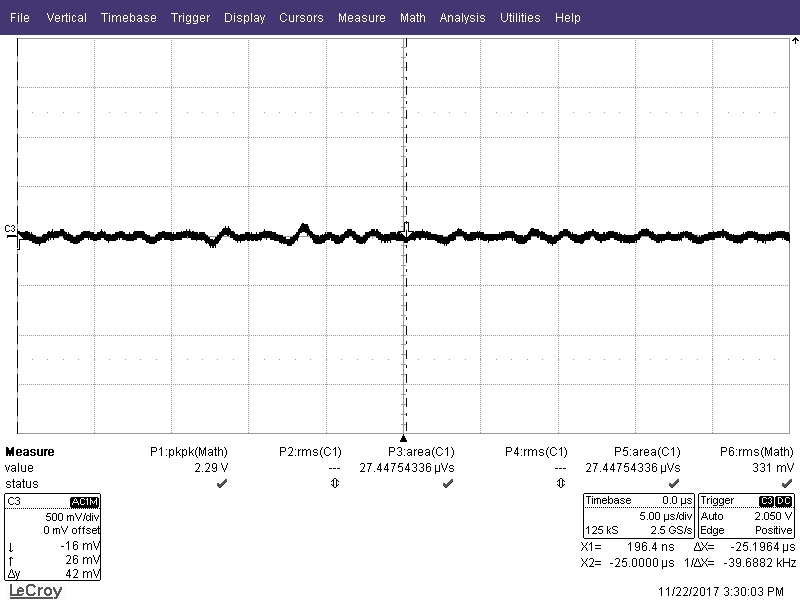

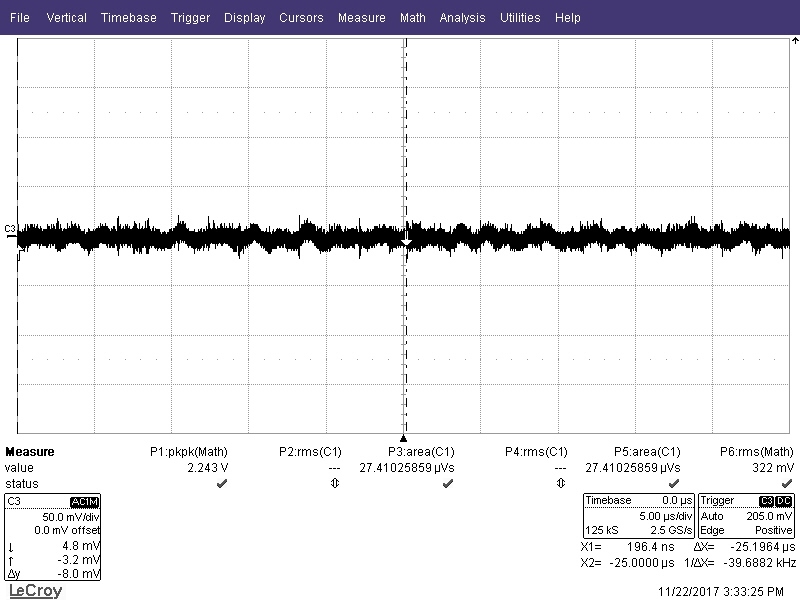

DAC线路上出现白色噪声问题。它似乎是白色噪声。当音频播放到DAC时,我们可以听到音频,但白色噪声始终存在。我们正在将所有0xXFx发送到TX样本的编解码器,因此不会 我们正在尝试播放的信号(很难将0弄乱)。如果我将编解码器静音,它将消失,如果我将增益应用到DAC将出现。我应用到DAC的增益量对噪声振幅没有影响。

我应该提到这是使用此编解码器的前几天,因此我无论如何都不是专家。

我们正在使用(用于输入) Line1L,Line1R,Line2R,Line2L和(用于输出) Mono_LO,HPROUT/COM,Right_LO,Left_LO

以下是设置和设置顺序:

REG 15 <- 0x80 (静音)

REG 16 <- 0x80 (静音)

REG 43 <- 0x80 (静音)

REG 44 <- 0x80 (静音)

第2条<- 0xAA (FS/6)

REG 5 <- 0

REG 6 <- 0 (D=0)

REG 4 <- 0x10 (J=16)

REG 11 <- 1 (R = 1)

第3条<-1 (P = 1)

REG 25 <- 0x40 (2V微偏)

REG 19 <- 0xFF (Line1L差动,左ADC通电,左ADC无软步进,Line1L未连接左ADC)

REG 22 <- 0xFF (线路1r差分,右侧ADC通电,右侧ADC无软设置,线路1R未连接右侧ADC)

REG 23 <- 0x80 (line2R差分)

REG 78 <- 0x80 (DACR1至MONO_LO)

REG 89 <- 0x80 (DACL1至RIGHT _LO)

REG 61 <- 0x80 (DACL1至HPROUT)

REG 37 <- 0xC0 (右侧和左侧DAC通电)

REG 79 <- 0x09 (MONO_LO已通电,未静音)

REG 7 <- 0x0A (启用右侧和左侧数据路径)

REG 9 <- 0x40 (DSP模式)

REG 8 <- 0xD0 (BCLK和WCLK输出,启用时钟以运行)

一个输入始终打开,以便进行设置

REG 16 <- 0 (右侧ADC +0dB)

在板上执行操作时,系统将选择特定输出:

我们为一项投入正确设定了收益

REG 16 <- 15 (右侧ADC +7.5dB)

然后我们为另一组设定增益

REG 43 <- 0x80 (左DAC静音)

REG 20 <- 0xFC (从左ADC,Line2L差动,左ADC偏置到共模电压-对于CYA取消路由,是否需要?)

REG 21 <- 0x78 (Unroute Line1R Off Left ADC - Unroute for a CYA,是否需要此项?)

REG 41 <- 0x40 (左DAC至左侧线路输出DAC_L3)

REG 19 <- 0x87 (Line1L差动,左ADC通电,左ADC无软步进)

REG 65 <- 0 (断电HPROUT)

REG 93 <- 0 (关闭右下加电)

REG 86 <- 0x09 (LET_LO取消静音,已通电)

REG 15 <- 0x0F (设置ADC=7.5dB)

REG 43 <- 60 (左DAC衰减-30dB)

和白噪声。由于我是这种编解码器的新手,所以我不知道是否缺少设置。我没有打开任何过滤或AGC, 在查看了所有向我跳出来的寄存器是否有噪音后,我没有看到任何设置。如果是主板噪音,我不是要求您修复我的主板, 但如果我缺少重要设置或编解码器设置错误,我肯定会知道。谢谢。